Nature Electronics ( IF 33.7 ) Pub Date : 2019-12-09 , DOI: 10.1038/s41928-019-0331-1 Loai Danial , Evgeny Pikhay , Eric Herbelin , Nicolas Wainstein , Vasu Gupta , Nimrod Wald , Yakov Roizin , Ramez Daniel , Shahar Kvatinsky

|

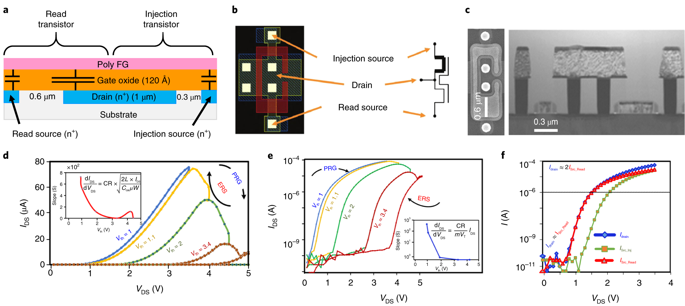

Metal–oxide memristive integrated technologies for analogue neuromorphic computing have undergone notable developments in the past decade, but are still not mature enough for very large-scale integration with complementary metal–oxide–semiconductor (CMOS) processes. Although non-volatile floating-gate synapse transistors are a more advanced technology embedded within CMOS processes, their performance as analogue resistive memories remains limited. Here, we report a low-power, two-terminal floating-gate transistor fabricated using standard single-poly technology in a commercial 180 nm CMOS process. Our device, which is integrated with a readout transistor, can operate in an energy-efficient subthreshold memristive mode. At the same time, it is linearized for small-signal changes with a two-orders-of-magnitude resistance dynamic range. Our device can be precisely tuned using optimized switching voltages and times, and can achieve 65 distinct resistive levels and ten-year analogue data retention. We experimentally demonstrate the feasibility of a selector-free integrated memristive array in basic neuromorphic applications, including spike-time-dependent plasticity, vector-matrix multiplication, associative memory and classification training.

中文翻译:

具有低功耗忆阻工作模式的两端浮栅晶体管,用于模拟神经形态计算

在过去的十年中,用于模拟神经形态计算的金属氧化物忆阻集成技术取得了显着发展,但仍不足以与互补金属氧化物半导体(CMOS)工艺进行大规模集成。尽管非易失性浮栅突触晶体管是CMOS工艺中嵌入的更先进的技术,但其作为模拟电阻式存储器的性能仍然受到限制。在这里,我们报道了一种低功耗,两端浮栅晶体管,该晶体管是在商业180 nm CMOS工艺中使用标准的单多晶硅技术制造的。我们的设备与一个读出晶体管集成在一起,可以在节能的亚阈值忆阻模式下工作。同时,它针对具有两个数量级电阻动态范围的小信号变化而线性化。我们的设备可以使用优化的开关电压和时间进行精确调整,并可以实现65种不同的电阻水平和十年的模拟数据保留。我们通过实验证明了在基本神经形态学应用中,无选择器的集成忆阻阵列的可行性,包括依赖于尖峰时间的可塑性,向量矩阵乘法,联想记忆和分类训练。

京公网安备 11010802027423号

京公网安备 11010802027423号