Our official English website, www.x-mol.net, welcomes your

feedback! (Note: you will need to create a separate account there.)

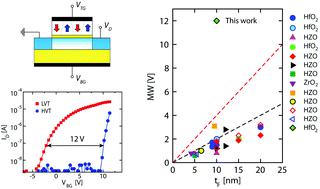

Ferroelectric transistors with asymmetric double gate for memory window exceeding 12 V and disturb-free read

Nanoscale ( IF 5.8 ) Pub Date : 2021-09-13 , DOI: 10.1039/d1nr05107e Halid Mulaosmanovic 1 , Dominik Kleimaier 2 , Stefan Dünkel 2 , Sven Beyer 2 , Thomas Mikolajick 1, 3 , Stefan Slesazeck 1

Nanoscale ( IF 5.8 ) Pub Date : 2021-09-13 , DOI: 10.1039/d1nr05107e Halid Mulaosmanovic 1 , Dominik Kleimaier 2 , Stefan Dünkel 2 , Sven Beyer 2 , Thomas Mikolajick 1, 3 , Stefan Slesazeck 1

Affiliation

|

Ferroelectric field-effect transistors (FeFETs) with a single gate structure and using the newly discovered ferroelectric hafnium oxide as an active material are attracting considerable interest for nonvolatile memory devices. However, such FeFETs struggle to achieve a large separation between the two logic states (memory window, MW) because of the thickness limitations of the ferroelectric film. Moreover, they are affected by detrimental disturbs coming from the read operation because of the shared write and read paths. Therefore, significant performance improvements are needed for the device to compete with established memory technologies like flash. Here, we present an asymmetric double-gate FeFET structure, where only one gate stack comprises the ferroelectric layer. We propose a novel read operation at the non-ferroelectric gate and demonstrate an amplified MW exceeding 12 V thanks to the enhanced body effect factor and the increased sensitivity of the transfer characteristics to the ferroelectric polarization. As a result, the above physical limitation is circumvented, thus by far outperforming the MW values reported in the literature. Based on this, we implement the multi-level cell storage featuring 4 bits per cell and stable data retention. Finally, an essential benefit originating from the separated write and read paths in our structure is exploited to demonstrate the fully disturb-free read operation. Besides memory, this could be particularly favorable for those neuromorphic and in-memory computing concepts with an occasional update of the stored variable but a very frequent read.

中文翻译:

具有非对称双栅极的铁电晶体管,用于超过 12 V 的存储器窗口和无干扰读取

具有单栅极结构并使用新发现的铁电氧化铪作为活性材料的铁电场效应晶体管 (FeFET) 引起了非易失性存储器件的极大兴趣。然而,由于铁电薄膜的厚度限制,此类 FeFET 难以实现两个逻辑状态(存储器窗口,MW)之间的较大分离。此外,由于共享的写入和读取路径,它们会受到来自读取操作的有害干扰的影响。因此,设备需要显着提高性能才能与闪存等成熟的内存技术竞争。在这里,我们提出了一种非对称双栅 FeFET 结构,其中只有一个栅叠层包含铁电层。我们在非铁电门上提出了一种新颖的读取操作,并证明了由于增强的体效应因子和对铁电极化的转移特性的敏感性增加,放大的 MW 超过了 12 V。结果,上述物理限制被规避,因此远远超过文献中报道的 MW 值。基于此,我们实现了多级单元存储,每个单元 4 位,数据保持稳定。最后,利用我们结构中分离的写入和读取路径所带来的基本好处来演示完全无干扰的读取操作。除了内存之外,这对于那些偶尔更新存储变量但非常频繁读取的神经形态和内存计算概念可能特别有利。

更新日期:2021-09-22

中文翻译:

具有非对称双栅极的铁电晶体管,用于超过 12 V 的存储器窗口和无干扰读取

具有单栅极结构并使用新发现的铁电氧化铪作为活性材料的铁电场效应晶体管 (FeFET) 引起了非易失性存储器件的极大兴趣。然而,由于铁电薄膜的厚度限制,此类 FeFET 难以实现两个逻辑状态(存储器窗口,MW)之间的较大分离。此外,由于共享的写入和读取路径,它们会受到来自读取操作的有害干扰的影响。因此,设备需要显着提高性能才能与闪存等成熟的内存技术竞争。在这里,我们提出了一种非对称双栅 FeFET 结构,其中只有一个栅叠层包含铁电层。我们在非铁电门上提出了一种新颖的读取操作,并证明了由于增强的体效应因子和对铁电极化的转移特性的敏感性增加,放大的 MW 超过了 12 V。结果,上述物理限制被规避,因此远远超过文献中报道的 MW 值。基于此,我们实现了多级单元存储,每个单元 4 位,数据保持稳定。最后,利用我们结构中分离的写入和读取路径所带来的基本好处来演示完全无干扰的读取操作。除了内存之外,这对于那些偶尔更新存储变量但非常频繁读取的神经形态和内存计算概念可能特别有利。

京公网安备 11010802027423号

京公网安备 11010802027423号