当前位置:

X-MOL 学术

›

Int. J. Circ. Theory Appl.

›

论文详情

Our official English website, www.x-mol.net, welcomes your

feedback! (Note: you will need to create a separate account there.)

A scalable high-speed hybrid 1-bit full adder design using XOR-XNOR module

International Journal of Circuit Theory and Applications ( IF 1.6 ) Pub Date : 2021-07-22 , DOI: 10.1002/cta.3109 Mehedi Hasan , Sharnali Islam , Mainul Hossain , Hasan U. Zaman

International Journal of Circuit Theory and Applications ( IF 1.6 ) Pub Date : 2021-07-22 , DOI: 10.1002/cta.3109 Mehedi Hasan , Sharnali Islam , Mainul Hossain , Hasan U. Zaman

|

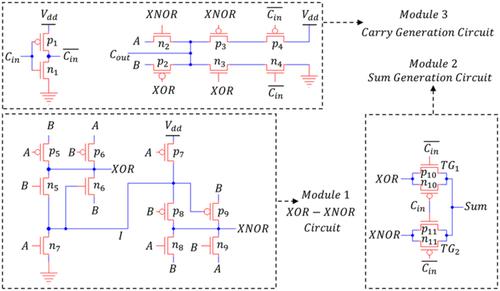

High-speed XOR-XNOR-based hybrid full adder (FA) using a combination of three logic techniques (transmission gate [TG], conventional CMOS [CCMOS], pass transistor [PT]) is presented in this work. Performance analysis and validation of the FA design presented in this work have been realized with reference to 10 state-of-the-art FAs. The scalability of the design has been tested by extending FA up to 32-bits in ripple carry adder (RCA) style. It has been observed that only four existing FAs and the proposed FA could be scaled up to 32-bits without including voltage restoration buffers in the internal stages. The proposed XOR-XNOR-based FA showed excellent performance metrics, both as a 1-bit adder cell as well as in wide word length adder form. Hence, the proposed XOR-XNOR-based hybrid FA can serve as a better alternative to the existing FAs in digital arithmetic blocks of modern microprocessors.

中文翻译:

使用 XOR-XNOR 模块的可扩展高速混合 1 位全加器设计

这项工作介绍了使用三种逻辑技术(传输门 [TG]、传统 CMOS [CCMOS]、传输晶体管 [PT])组合的基于 XOR-XNOR 的高速混合全加器 (FA)。这项工作中提出的 FA 设计的性能分析和验证已经参考 10 个最先进的 FA 实现。该设计的可扩展性已经通过以纹波进位加法器 (RCA) 样式将 FA 扩展到 32 位进行了测试。已经观察到只有四个现有的 FA 和提议的 FA 可以扩展到 32 位,而无需在内部阶段包括电压恢复缓冲器。提议的基于 XOR-XNOR 的 FA 表现出出色的性能指标,无论是作为 1 位加法器单元还是宽字长加法器形式。因此,

更新日期:2021-07-22

中文翻译:

使用 XOR-XNOR 模块的可扩展高速混合 1 位全加器设计

这项工作介绍了使用三种逻辑技术(传输门 [TG]、传统 CMOS [CCMOS]、传输晶体管 [PT])组合的基于 XOR-XNOR 的高速混合全加器 (FA)。这项工作中提出的 FA 设计的性能分析和验证已经参考 10 个最先进的 FA 实现。该设计的可扩展性已经通过以纹波进位加法器 (RCA) 样式将 FA 扩展到 32 位进行了测试。已经观察到只有四个现有的 FA 和提议的 FA 可以扩展到 32 位,而无需在内部阶段包括电压恢复缓冲器。提议的基于 XOR-XNOR 的 FA 表现出出色的性能指标,无论是作为 1 位加法器单元还是宽字长加法器形式。因此,

京公网安备 11010802027423号

京公网安备 11010802027423号