当前位置:

X-MOL 学术

›

Int. J. Circ. Theory Appl.

›

论文详情

Our official English website, www.x-mol.net, welcomes your

feedback! (Note: you will need to create a separate account there.)

An error efficient and low complexity approximate multi-bit adder for image processing applications

International Journal of Circuit Theory and Applications ( IF 1.8 ) Pub Date : 2021-06-03 , DOI: 10.1002/cta.3074 M. Priyadharshni 1 , Antra Raj Gupta 2 , V. Nithish Kumar 1 , S. Kumaravel 1

International Journal of Circuit Theory and Applications ( IF 1.8 ) Pub Date : 2021-06-03 , DOI: 10.1002/cta.3074 M. Priyadharshni 1 , Antra Raj Gupta 2 , V. Nithish Kumar 1 , S. Kumaravel 1

Affiliation

|

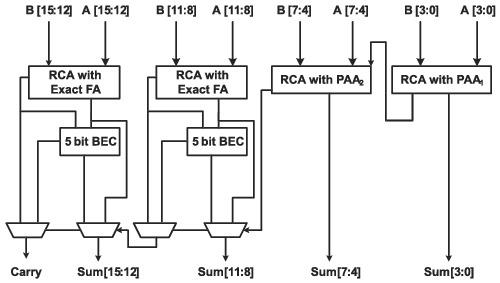

Approximate computing-based hardware is directed towards reduction in area and power consumption; it finds better suitability in various image processing applications. In order to achieve low complexity, approximate techniques are applied in the arithmetic units which provide promising results in enhancing the performance of DSP processors with optimal degradation on its accuracy. In this paper, two approximate full adder designs are proposed, namely, the first design as proposed approximate full adder 1 (PAA1) and the second design as proposed approximate full adder 2 (PAA2). In both the designs, the approximation on the Boolean expressions is carried out to reduce the hardware complexity with the significant tolerance on the error rate. Also, a multi-bit approximate carry select adder is proposed with the utilization of PAA1 and PAA2, respectively. The performance of the proposed adders is analyzed in terms of parameters like gate count, structural synthesis, error, and also in terms of image metrics. The proposed and existing designs are synthesized using Synopsys Design Compiler with TSMC 65 nm technology for better comparison. Synthesis results indicate that the proposed 16-bit approximate carry select adder (CSLA) shows a significant reduction of 58% in area delay product and 70% in power delay product, in comparison with the conventional CSLA. The image metrics results also validate that the proposed adder with highest peak signal-to-noise ratio is highly adoptable for image processing applications.

中文翻译:

一种用于图像处理应用的错误高效且低复杂度的近似多位加法器

近似的基于计算的硬件旨在减少面积和功耗;它更适用于各种图像处理应用。为了实现低复杂度,在算术单元中应用了近似技术,这在增强 DSP 处理器性能方面提供了有希望的结果,同时优化了其精度。在本文中,提出了两种近似全加器设计,即第一种设计为提议的近似全加器 1 ( P A A 1 ) 和第二种设计为提议的近似全加器 2 ( P A A 2)。在这两种设计中,对布尔表达式进行近似以降低硬件复杂性,同时对错误率具有显着的容忍度。此外,提出了一种利用P A A 1和P A A 2的多位近似进位选择加法器, 分别。建议的加法器的性能根据门数、结构合成、误差等参数以及图像指标进行分析。建议和现有设计使用具有 TSMC 65 nm 技术的 Synopsys Design Compiler 进行综合,以便更好地进行比较。综合结果表明,与传统的 CSLA 相比,所提出的 16 位近似进位选择加法器 (CSLA) 显着减少了 58% 的面积延迟积和 70% 的功率延迟积。图像度量结果还验证了所提出的具有最高峰值信噪比的加法器非常适用于图像处理应用。

更新日期:2021-08-12

中文翻译:

一种用于图像处理应用的错误高效且低复杂度的近似多位加法器

近似的基于计算的硬件旨在减少面积和功耗;它更适用于各种图像处理应用。为了实现低复杂度,在算术单元中应用了近似技术,这在增强 DSP 处理器性能方面提供了有希望的结果,同时优化了其精度。在本文中,提出了两种近似全加器设计,即第一种设计为提议的近似全加器 1 ( P A A 1 ) 和第二种设计为提议的近似全加器 2 ( P A A 2)。在这两种设计中,对布尔表达式进行近似以降低硬件复杂性,同时对错误率具有显着的容忍度。此外,提出了一种利用P A A 1和P A A 2的多位近似进位选择加法器, 分别。建议的加法器的性能根据门数、结构合成、误差等参数以及图像指标进行分析。建议和现有设计使用具有 TSMC 65 nm 技术的 Synopsys Design Compiler 进行综合,以便更好地进行比较。综合结果表明,与传统的 CSLA 相比,所提出的 16 位近似进位选择加法器 (CSLA) 显着减少了 58% 的面积延迟积和 70% 的功率延迟积。图像度量结果还验证了所提出的具有最高峰值信噪比的加法器非常适用于图像处理应用。

京公网安备 11010802027423号

京公网安备 11010802027423号