当前位置:

X-MOL 学术

›

Int. J. Circ. Theory Appl.

›

论文详情

Our official English website, www.x-mol.net, welcomes your

feedback! (Note: you will need to create a separate account there.)

Field-programmable gate array-based design for real-time computation of ensemble empirical mode decomposition

International Journal of Circuit Theory and Applications ( IF 1.8 ) Pub Date : 2021-04-27 , DOI: 10.1002/cta.3028 Kaushik Das 1 , Sambhu Nath Pradhan 1

International Journal of Circuit Theory and Applications ( IF 1.8 ) Pub Date : 2021-04-27 , DOI: 10.1002/cta.3028 Kaushik Das 1 , Sambhu Nath Pradhan 1

Affiliation

|

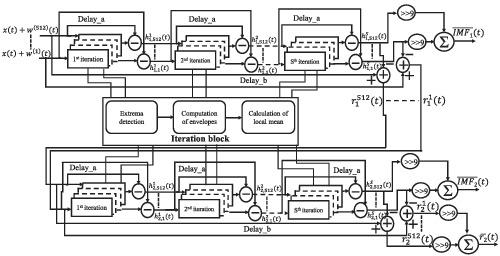

Empirical mode decomposition (EMD) is considered as a suitable method when the signal to be analyzed is nonlinear or nonstationary in nature. But, EMD suffers from a problem known as mode mixing. To, reduce this problem, ensemble EMD (EEMD) was proposed. In this paper, we have presented a fast field-programmable gate array (FPGA)-based design for EEMD. Where calculation of output can be done in a parallel manner for different realizations. The design has a comparatively less execution time, and the execution time of the proposed EEMD design is even less than some state-of-the-art EMD-based design, although the architecture of EEMD is more complex, when compared with the EMD design. In this work, we have also performed an FPGA implementation of the EMD algorithm. The root mean square error (RMSE) and the correlation values of the intrinsic mode function (IMFs) obtained from the proposed EMD and EEMD designs are compared. The proposed FPGA-based architecture of the EEMD algorithm is designed using Verilog-hardware description language (HDL) and implemented on a Kintex-7 FPGA. The EEMD architecture consists of cubic Hermite spline interpolation (CHSI) and cubic spline interpolation (CSI) for the envelope generation.

中文翻译:

基于现场可编程门阵列的集成经验模式分解实时计算设计

当要分析的信号本质上是非线性或非平稳时,经验模态分解 (EMD) 被认为是一种合适的方法。但是,EMD 存在称为模式混合的问题。为了减少这个问题,提出了集成 EMD (EEMD)。在本文中,我们提出了一种基于现场可编程门阵列 (FPGA) 的快速 EEMD 设计。对于不同的实现,可以以并行方式计算输出。该设计的执行时间相对较短,所提出的 EEMD 设计的执行时间甚至比一些最先进的基于 EMD 的设计还要短,尽管与 EMD 设计相比,EEMD 的架构更为复杂. 在这项工作中,我们还执行了 EMD 算法的 FPGA 实现。比较了从建议的 EMD 和 EEMD 设计中获得的均方根误差 (RMSE) 和固有模式函数 (IMF) 的相关值。所提出的基于 FPGA 的 EEMD 算法架构是使用 Verilog 硬件描述语言 (HDL) 设计的,并在 Kintex-7 FPGA 上实现。EEMD 架构由三次 Hermite 样条插值 (CHSI) 和三次样条插值 (CSI) 组成,用于生成包络。

更新日期:2021-04-27

中文翻译:

基于现场可编程门阵列的集成经验模式分解实时计算设计

当要分析的信号本质上是非线性或非平稳时,经验模态分解 (EMD) 被认为是一种合适的方法。但是,EMD 存在称为模式混合的问题。为了减少这个问题,提出了集成 EMD (EEMD)。在本文中,我们提出了一种基于现场可编程门阵列 (FPGA) 的快速 EEMD 设计。对于不同的实现,可以以并行方式计算输出。该设计的执行时间相对较短,所提出的 EEMD 设计的执行时间甚至比一些最先进的基于 EMD 的设计还要短,尽管与 EMD 设计相比,EEMD 的架构更为复杂. 在这项工作中,我们还执行了 EMD 算法的 FPGA 实现。比较了从建议的 EMD 和 EEMD 设计中获得的均方根误差 (RMSE) 和固有模式函数 (IMF) 的相关值。所提出的基于 FPGA 的 EEMD 算法架构是使用 Verilog 硬件描述语言 (HDL) 设计的,并在 Kintex-7 FPGA 上实现。EEMD 架构由三次 Hermite 样条插值 (CHSI) 和三次样条插值 (CSI) 组成,用于生成包络。

京公网安备 11010802027423号

京公网安备 11010802027423号