Microelectronic Engineering ( IF 2.6 ) Pub Date : 2021-01-13 , DOI: 10.1016/j.mee.2021.111509 Shuxiao Wang , Qing Wang , Yufei Liu , Lianxi Jia , Mingbin Yu , Peng Sun , Fei Geng , Yan Cai , Zhijuan Tu

|

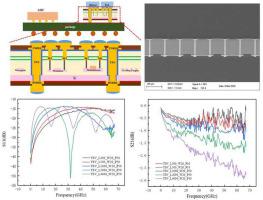

The optoelectronic hybrid integration based on co-package has attracted much attention to meet the requirements of high-performance chip development and functional integration. TSVs and redistribution layers (RDLs) are of great importance for both the packaging process and the system design of 3D integration. This paper presents the measurements and analysis of TSV and RDL test structures, from DC to high frequency up to 67 GHz. TSVs and RDLs with low insertion loss up to 67 GHz are demonstrated and the impact of TSV arrangements on the transmission performance are analysed. The insertion loss of a 500 μm long coplanar waveguide (CPW) transmission line of frontside RDL (FSRDL) is 0.75 dB at 67 GHz. The insertion loss is less than 1 dB at 67 GHz for a TSV-RDL signal path with the length of 500 μm.

中文翻译:

低损耗硅通孔(TSV)和传输线,用于3D光电集成

基于协同封装的光电子混合集成已经引起了人们的广泛关注,以满足高性能芯片开发和功能集成的要求。TSV和重新分发层(RDL)对于3D集成的打包过程和系统设计都非常重要。本文介绍了从直流到高达67 GHz的TSV和RDL测试结构的测量和分析。演示了具有高达67 GHz的低插入损耗的TSV和RDL,并分析了TSV布置对传输性能的影响。前端RDL(FSRDL)的500μm长的共面波导(CPW)传输线在67 GHz时的插入损耗为0.75 dB。对于长度为500μm的TSV-RDL信号路径,插入损耗在67 GHz时小于1 dB。

京公网安备 11010802027423号

京公网安备 11010802027423号