当前位置:

X-MOL 学术

›

Int. J. Circ. Theory Appl.

›

论文详情

Our official English website, www.x-mol.net, welcomes your

feedback! (Note: you will need to create a separate account there.)

A 12‐Gb/s serial link transceiver using dual‐mode pulse amplitude modulation scheme in a 0.18‐μm CMOS process

International Journal of Circuit Theory and Applications ( IF 1.8 ) Pub Date : 2021-01-06 , DOI: 10.1002/cta.2922 Neda Mohabbatian 1 , Khayrollah Hadidi 1

International Journal of Circuit Theory and Applications ( IF 1.8 ) Pub Date : 2021-01-06 , DOI: 10.1002/cta.2922 Neda Mohabbatian 1 , Khayrollah Hadidi 1

Affiliation

|

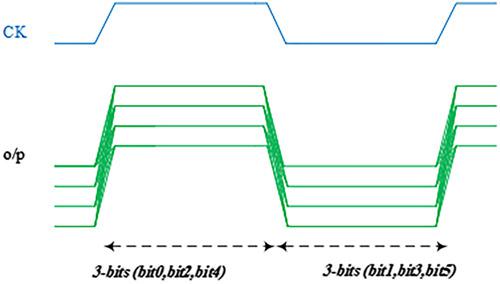

A 12‐Gb/s 0.18‐μm complementary metal oxide semiconductor (CMOS) serial link transceiver with embedded clock signal in data stream using dual‐mode pulse amplitude modulation is presented. The 6‐bit data and the clock signal are both transferred through the same transmission channel. In the proposed modulation technique, the clock signal is easily recovered using a conventional phase‐locked loop without any complex encoders in the transmitter circuit. The transmitter includes multiplexers, an output driver, and pre‐emphasis circuitry with 127‐mW power consumption. The receiver is composed of a phase‐locked loop for clock recovery and demodulator blocks for data recovery, and it dissipates 45 mW of power.

中文翻译:

在0.18μmCMOS工艺中使用双模式脉冲幅度调制方案的12Gb / s串行链路收发器

A 12-Gb / s的0.18 μ米,在数据嵌入时钟信号流采用双模式脉冲幅度调制被呈现互补金属氧化物半导体(CMOS)串行链路的收发器。6位数据和时钟信号都通过同一传输通道传输。在提出的调制技术中,可以使用常规锁相环轻松恢复时钟信号,而无需在发送器电路中使用任何复杂的编码器。发送器包括多路复用器,输出驱动器和功耗为127mW的预加重电路。接收器由用于时钟恢复的锁相环和用于数据恢复的解调器模块组成,其功耗为45 mW。

更新日期:2021-02-21

中文翻译:

在0.18μmCMOS工艺中使用双模式脉冲幅度调制方案的12Gb / s串行链路收发器

A 12-Gb / s的0.18 μ米,在数据嵌入时钟信号流采用双模式脉冲幅度调制被呈现互补金属氧化物半导体(CMOS)串行链路的收发器。6位数据和时钟信号都通过同一传输通道传输。在提出的调制技术中,可以使用常规锁相环轻松恢复时钟信号,而无需在发送器电路中使用任何复杂的编码器。发送器包括多路复用器,输出驱动器和功耗为127mW的预加重电路。接收器由用于时钟恢复的锁相环和用于数据恢复的解调器模块组成,其功耗为45 mW。

京公网安备 11010802027423号

京公网安备 11010802027423号