当前位置:

X-MOL 学术

›

Int. J. Circ. Theory Appl.

›

论文详情

Our official English website, www.x-mol.net, welcomes your

feedback! (Note: you will need to create a separate account there.)

Low‐voltage and high‐speed stand‐alone multiple‐input complex gates for error correction coding applications

International Journal of Circuit Theory and Applications ( IF 1.8 ) Pub Date : 2020-12-28 , DOI: 10.1002/cta.2927 Maliheh Rafiee 1 , Mohammad‐Bagher Ghaznavi‐Ghoushchi 1

International Journal of Circuit Theory and Applications ( IF 1.8 ) Pub Date : 2020-12-28 , DOI: 10.1002/cta.2927 Maliheh Rafiee 1 , Mohammad‐Bagher Ghaznavi‐Ghoushchi 1

Affiliation

|

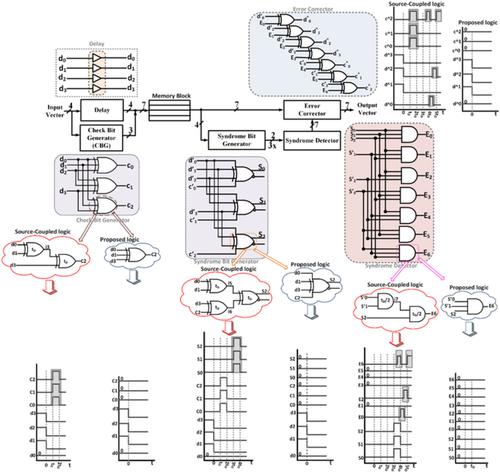

This paper presents two low‐voltage high‐speed shallow‐depth current mode logic (CML) topologies. The number of stacked transistors of these proposed structures decreases between VDD to GND. Reduce stacks in proposed gates enhance the circuit to operate at lower supply voltages. Therefore, the proposed logic causes to use of a stand‐alone multiple‐input gate instead of a low‐input gate. The use of decomposing multiple‐input gate for some input series causes error in the output of the circuit. In advanced technologies with size scaling down, the reliability and correctness of data in memories are essential issues. Error correction codes (ECCs) are used for protecting memories against faults. Reducing power consumption with preserving speed is vital in the design of ECCs. The units of ECCs are composed of multiple‐input gates; hence, using a low‐voltage high‐performance structure is required. The essential properties of the proposed logic are low‐voltage and high‐speed operation modes. It also gains in delay improvement of the proposed structure and multiple‐tailed current mode logic (MTCML) than source‐coupled logic (SCL) about 27% and 21% in the low‐voltage design. The final power delay product (PDP) of proposed logic and MTCML is improved by about 14% and 11% than SCL.

中文翻译:

低压和高速独立多输入复杂门,用于纠错编码应用

本文介绍了两种低压高速浅深度电流模式逻辑(CML)拓扑。这些建议结构的堆叠晶体管数量在V DD之间减少到GND。减少拟议栅极中的堆叠,可增强电路以较低的电源电压工作。因此,提出的逻辑导致使用独立的多输入门而不是低输入门。对某些输入序列使用多输入门分解会导致电路输出错误。在尺寸缩小的先进技术中,存储器中数据的可靠性和正确性是至关重要的问题。纠错码(ECC)用于保护存储器免于故障。在保持ECC速度的同时,降低功耗和保持速度至关重要。ECC的单元由多输入门组成。因此,需要使用低压高性能结构。所提出的逻辑的基本特性是低电压和高速操作模式。与低电压设计中的源极耦合逻辑(SCL)相比,与传统的源极耦合逻辑(SCL)相比,该方法在结构和多尾电流模式逻辑(MTCML)方面的延迟改进也有所提高。所提出的逻辑和MTCML的最终功率延迟乘积(PDP)比SCL分别提高了约14%和11%。

更新日期:2020-12-28

中文翻译:

低压和高速独立多输入复杂门,用于纠错编码应用

本文介绍了两种低压高速浅深度电流模式逻辑(CML)拓扑。这些建议结构的堆叠晶体管数量在V DD之间减少到GND。减少拟议栅极中的堆叠,可增强电路以较低的电源电压工作。因此,提出的逻辑导致使用独立的多输入门而不是低输入门。对某些输入序列使用多输入门分解会导致电路输出错误。在尺寸缩小的先进技术中,存储器中数据的可靠性和正确性是至关重要的问题。纠错码(ECC)用于保护存储器免于故障。在保持ECC速度的同时,降低功耗和保持速度至关重要。ECC的单元由多输入门组成。因此,需要使用低压高性能结构。所提出的逻辑的基本特性是低电压和高速操作模式。与低电压设计中的源极耦合逻辑(SCL)相比,与传统的源极耦合逻辑(SCL)相比,该方法在结构和多尾电流模式逻辑(MTCML)方面的延迟改进也有所提高。所提出的逻辑和MTCML的最终功率延迟乘积(PDP)比SCL分别提高了约14%和11%。

京公网安备 11010802027423号

京公网安备 11010802027423号