Microelectronics Journal ( IF 1.9 ) Pub Date : 2020-12-07 , DOI: 10.1016/j.mejo.2020.104947 Sir Orlando Verducci , Duarte L. Oliveira , Gracieth C. Batista , Tiago S. Curtinhas

|

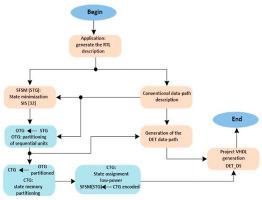

The continuous search for higher performances and low power dissipation on digital systems shows to be critical. The pipeline control is a good alternative for achieving good results, but the activity of the clock is responsible for the high consumption of 15–45% of the total circuit energy. Decreasing the clock activity leads not only to a reduction of this consumption but also to a reduction of noise and electromagnetic interference. An interesting approach to achieve this goal is the design of synchronous digital systems that operate in both edges of the clock signal (double-edge triggered – DET), allowing a reduction of 50% in the operating frequency while maintains the same data processing rate. As we know, the use of double-edge triggered flip-flops (DET-FF) leads to some main drawbacks. Then, in this paper, we propose a novel method that allows synthesizing synchronous digital systems with pipeline control. Such control operates in both edges of the clock using only standards flip-flops (single-edge triggered flip-flops-SET-FF) as components of the state memories. The method was validated for a well-known example (second order differential equation solver), and it was applied to a set of 5 well-known benchmarks, showing a mean reduction of 53% in latency time when compared to conventional methods working at the same frequency (in the case 50MHZ). We achieved an average reduction of 10% in latency time when the operating frequency of our projects was reduced to 25MHZ and compared to conventional ones at 50MHZ. The proposed method leads to a mean reduction of 45% in dynamic power consumption when compared to conventional ones. These results, although presenting a minimum area penalty, show a high potential of practical implementations focusing on low-power and high performances.

中文翻译:

设计在时钟双沿运行的低功率流水线同步系统的新颖方法

在数字系统上不断寻求更高性能和低功耗非常关键。管道控制是获得良好结果的不错选择,但是时钟的活动导致了总电路能量的15%至45%的高消耗。时钟活动性的降低不仅导致功耗的降低,而且还降低了噪声和电磁干扰。实现此目标的一种有趣方法是设计在时钟信号的两个边沿(双沿触发– DET)中工作的同步数字系统,从而可以将工作频率降低50%,同时保持相同的数据处理速率。众所周知,使用双沿触发触发器(DET-FF)会带来一些主要缺点。然后,在本文中 我们提出了一种新颖的方法,该方法允许使用流水线控制来合成同步数字系统。仅使用标准触发器(单沿触发触发器-SET-FF)作为状态存储器的组件,这样的控制在时钟的两个边缘中进行操作。该方法已针对一个著名示例(二阶微分方程求解器)进行了验证,并应用于一组5个著名基准,与传统方法相比,该方法在等待时间上平均减少了53%。相同的频率(在50MHZ的情况下)。当我们将项目的运行频率降低到25MHZ时,与传统的50MHZ相比,我们的延迟时间平均减少了10%。与传统方法相比,该方法可将动态功耗平均降低45%。这些结果,

京公网安备 11010802027423号

京公网安备 11010802027423号