当前位置:

X-MOL 学术

›

Int. J. Circ. Theory Appl.

›

论文详情

Our official English website, www.x-mol.net, welcomes your

feedback! (Note: you will need to create a separate account there.)

A high‐resolution hybrid digital pulse width modulator with dual‐edge‐triggered flip‐flops and hardware compensation

International Journal of Circuit Theory and Applications ( IF 1.8 ) Pub Date : 2020-09-27 , DOI: 10.1002/cta.2885 Xin Cheng 1 , Bin Li 1 , Haowen Zhu 1 , Yongqiang Zhang 1 , Zhang Zhang 1

International Journal of Circuit Theory and Applications ( IF 1.8 ) Pub Date : 2020-09-27 , DOI: 10.1002/cta.2885 Xin Cheng 1 , Bin Li 1 , Haowen Zhu 1 , Yongqiang Zhang 1 , Zhang Zhang 1

Affiliation

|

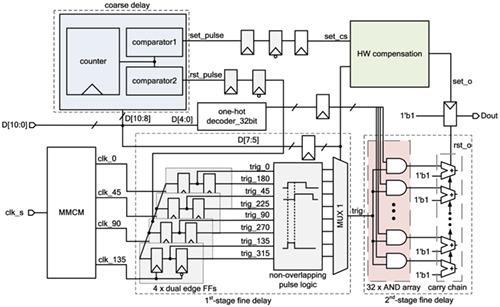

In this paper, a hybrid architecture of digital pulse width modulator (DPWM) which applies a counter, a phase‐shifted circuit, and a carry chain is proposed. Dual‐edge‐triggered flip‐flops are used in the phase‐shifted circuit to generate signals with 45° phase shift, which not only improves the resolution of the DPWM but also reduces the resource consumption in the carry chain. Furthermore, a hardware compensation method is used to solve the duty cycle increment phenomenon that affects the regulation accuracy of converter. An 11‐bit DPWM with the proposed architecture is implemented and tested by Xilinx Artix‐7 FPGA. The experimental results show a high resolution of 32 ps and a good linearity where R2 is 0.99 and verify the effect of duty cycle compensation.

中文翻译:

具有双沿触发触发器和硬件补偿的高分辨率混合数字脉冲宽度调制器

本文提出了一种采用计数器,相移电路和进位链的数字脉宽调制器(DPWM)的混合体系结构。相移电路中使用双沿触发触发器来产生具有45°相移的信号,这不仅提高了DPWM的分辨率,而且降低了进位链中的资源消耗。此外,使用硬件补偿方法来解决影响转换器调节精度的占空比增加现象。Xilinx Artix-7 FPGA实现并测试了具有建议架构的11位DPWM。实验结果表明,高分辨率(32 ps)和良好的线性度(R 2为0.99)证明了占空比补偿的效果。

更新日期:2020-09-27

中文翻译:

具有双沿触发触发器和硬件补偿的高分辨率混合数字脉冲宽度调制器

本文提出了一种采用计数器,相移电路和进位链的数字脉宽调制器(DPWM)的混合体系结构。相移电路中使用双沿触发触发器来产生具有45°相移的信号,这不仅提高了DPWM的分辨率,而且降低了进位链中的资源消耗。此外,使用硬件补偿方法来解决影响转换器调节精度的占空比增加现象。Xilinx Artix-7 FPGA实现并测试了具有建议架构的11位DPWM。实验结果表明,高分辨率(32 ps)和良好的线性度(R 2为0.99)证明了占空比补偿的效果。

京公网安备 11010802027423号

京公网安备 11010802027423号