当前位置:

X-MOL 学术

›

Trans. Emerg. Telecommun. Technol.

›

论文详情

Our official English website, www.x-mol.net, welcomes your

feedback! (Note: you will need to create a separate account there.)

Design of a high speed 14‐bit digital to analog converter circuit

Transactions on Emerging Telecommunications Technologies ( IF 2.5 ) Pub Date : 2020-07-13 , DOI: 10.1002/ett.4043 Yu‐Lan Tang 1 , Jian‐hui Chen 1 , Qian Ye 1

Transactions on Emerging Telecommunications Technologies ( IF 2.5 ) Pub Date : 2020-07-13 , DOI: 10.1002/ett.4043 Yu‐Lan Tang 1 , Jian‐hui Chen 1 , Qian Ye 1

Affiliation

|

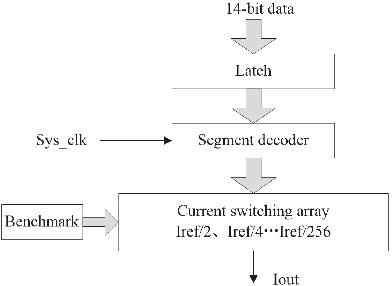

A 14‐bit current domain digital to analog converter (DAC) is presented, which employs 4 + 4 + 6 segmented current‐steering architecture. The high 4‐bit and intermediate 4‐bit adopted thermometer code control, and the low‐6 bit used direct control of binary weighted current source, so the dynamic performance of DAC is improved. The detailed design of the core modules of DAC is also given, including high‐precision programmable reference current source, DAC encoding and decoding circuit, and the current source array. The DAC is fabricated in SMIC 0.18 μm 1P6M CMOS technology. The simulation results of Hspice show that the spurious free dynamic range for 80 MHz output signal at 400 MHz sampling clock rate is 72.47 dB, and the design has met the requirements.

中文翻译:

高速14位数模转换器电路的设计

提出了一种14位电流域数模转换器(DAC),该转换器采用4 + 4 + 6分段电流控制架构。高4位和中间4位采用温度计代码控制,低6位采用二进制加权电流源的直接控制,因此DAC的动态性能得到改善。还给出了DAC核心模块的详细设计,包括高精度可编程参考电流源,DAC编码和解码电路以及电流源阵列。DAC采用SMIC 0.18μm1P6M CMOS技术制造。Hspice的仿真结果表明,在400 MHz采样时钟速率下,80 MHz输出信号的无杂散动态范围为72.47 dB,满足设计要求。

更新日期:2020-07-13

中文翻译:

高速14位数模转换器电路的设计

提出了一种14位电流域数模转换器(DAC),该转换器采用4 + 4 + 6分段电流控制架构。高4位和中间4位采用温度计代码控制,低6位采用二进制加权电流源的直接控制,因此DAC的动态性能得到改善。还给出了DAC核心模块的详细设计,包括高精度可编程参考电流源,DAC编码和解码电路以及电流源阵列。DAC采用SMIC 0.18μm1P6M CMOS技术制造。Hspice的仿真结果表明,在400 MHz采样时钟速率下,80 MHz输出信号的无杂散动态范围为72.47 dB,满足设计要求。

京公网安备 11010802027423号

京公网安备 11010802027423号