当前位置:

X-MOL 学术

›

Int. J. Circ. Theory Appl.

›

论文详情

Our official English website, www.x-mol.net, welcomes your

feedback! (Note: you will need to create a separate account there.)

Design of an 8‐bit time‐mode cyclic ADC based on macro modeling

International Journal of Circuit Theory and Applications ( IF 1.8 ) Pub Date : 2020-07-04 , DOI: 10.1002/cta.2842 Zaniar Hoseini 1 , Kye‐Shin Lee 2 , Chun Ki Kwon 3

International Journal of Circuit Theory and Applications ( IF 1.8 ) Pub Date : 2020-07-04 , DOI: 10.1002/cta.2842 Zaniar Hoseini 1 , Kye‐Shin Lee 2 , Chun Ki Kwon 3

Affiliation

|

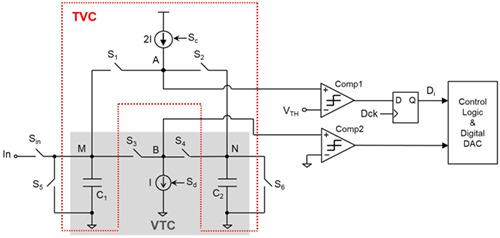

This work presents a macro modeling approach for the time‐mode cyclic ADC. The proposed ADC macro model is realized using the time‐to‐voltage converter (TVC) and the voltage‐to‐time converter (VTC) that are the key building blocks of time‐mode ADCs. In addition, the effect of circuit nonidealities and error sources of the time‐mode ADC including parasitic capacitance, current source output resistance, switch on‐resistance, capacitor mismatch, and comparator offset are incorporated in the macro model. The simulation time of the proposed ADC macro model showed 87.1% reduction compared to the all transistor level ADC circuit. As a result, the proposed ADC macro model can facilitate the ADC design and leverage the ADC nonideality analysis. Furthermore, the proposed macro model can be used for ADC calibration scheme development. As a practical design example, the macro model for an 8‐bit time‐mode cyclic ADC has been realized, where the nonideality analysis, design optimization, and calibration scheme development based on the proposed macro model have been demonstrated.

中文翻译:

基于宏建模的8位时间模式循环ADC的设计

这项工作提出了一种用于时间模式循环ADC的宏建模方法。拟议的ADC宏模型通过使用时间-电压转换器(TVC)和电压-时间转换器(VTC)来实现,它们是时间模式ADC的关键组成部分。此外,宏模型中还纳入了时间模式ADC的电路非理想性和误差源的影响,包括寄生电容,电流源输出电阻,开关导通电阻,电容器失配和比较器失调。与所有晶体管级ADC电路相比,所建议的ADC宏模型的仿真时间缩短了87.1%。结果,建议的ADC宏模型可以简化ADC设计并利用ADC非理想性分析。此外,提出的宏模型可用于ADC校准方案开发。

更新日期:2020-07-04

中文翻译:

基于宏建模的8位时间模式循环ADC的设计

这项工作提出了一种用于时间模式循环ADC的宏建模方法。拟议的ADC宏模型通过使用时间-电压转换器(TVC)和电压-时间转换器(VTC)来实现,它们是时间模式ADC的关键组成部分。此外,宏模型中还纳入了时间模式ADC的电路非理想性和误差源的影响,包括寄生电容,电流源输出电阻,开关导通电阻,电容器失配和比较器失调。与所有晶体管级ADC电路相比,所建议的ADC宏模型的仿真时间缩短了87.1%。结果,建议的ADC宏模型可以简化ADC设计并利用ADC非理想性分析。此外,提出的宏模型可用于ADC校准方案开发。

京公网安备 11010802027423号

京公网安备 11010802027423号