当前位置:

X-MOL 学术

›

Int. J. Circ. Theory Appl.

›

论文详情

Our official English website, www.x-mol.net, welcomes your

feedback! (Note: you will need to create a separate account there.)

Process‐induced variability modeling of subthreshold leakage power considering device stacking

International Journal of Circuit Theory and Applications ( IF 1.8 ) Pub Date : 2020-02-06 , DOI: 10.1002/cta.2755 Anala M. Reddy 1 , B.P. Harish 2

International Journal of Circuit Theory and Applications ( IF 1.8 ) Pub Date : 2020-02-06 , DOI: 10.1002/cta.2755 Anala M. Reddy 1 , B.P. Harish 2

Affiliation

|

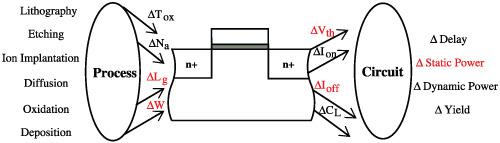

The dominance of leakage currents in circuit design has been impelled by steady downscaling of MOSFET into nanometer regime, and has become a significant component of total IC power dissipation. The issue is further aggravated with the inability to gauge the tolerance of process parameters around their nominal value. Consequently, the drive to improve the static power prediction has enticed accurate and reliable modeling of leakage current, specifically for ultralow power applications. In contrast to gate‐ and band‐to‐band‐tunneling leakages, subthreshold leakage exhibits high susceptibility to process variations and hence has been considered for variability modeling. Fluctuations in the device electrical and geometry parameters result in a wider distribution of subthreshold leakage current. Hence, taking into account stacking effect, an analytical variability model to estimate subthreshold leakage power in subthreshold circuits, in the presence of threshold voltage variations is proposed. Further, the impact of threshold voltage variability on subthreshold leakage power is modeled in conjunction with simultaneous variations in gate length and width. The leakage power variability is characterized by model‐generated distributions obtained using Monte Carlo analysis and validated against SPICE simulations. The proposed model is about 700

computationally faster than SPICE simulations with mean error being less than 0.19%.

computationally faster than SPICE simulations with mean error being less than 0.19%.

中文翻译:

考虑设备堆叠的亚阈值泄漏功率的过程诱导可变性建模

MOSFET的稳步降级为纳米级,已推动了电路设计中泄漏电流的支配,并已成为总IC功耗的重要组成部分。由于无法测量过程参数在其标称值附近的容忍度,这一问题进一步恶化。因此,改善静态功率预测的驱动力吸引了准确可靠的泄漏电流建模,特别是针对超低功耗应用。与门和带对隧道的泄漏相反,亚阈值泄漏对过程变化表现出很高的敏感性,因此已被考虑用于变化建模。器件电气和几何参数的波动导致亚阈值泄漏电流的分布更加广泛。因此,考虑到堆叠效应,提出了一种在阈值电压存在变化的情况下估计亚阈值电路中亚阈值泄漏功率的分析变异性模型。此外,结合栅极长度和宽度的同时变化,对阈值电压可变性对亚阈值泄漏功率的影响进行了建模。泄漏功率变异性的特征在于模型生成的分布,这些分布是使用蒙特卡洛分析获得的,并针对SPICE仿真进行了验证。拟议的模型约为700 泄漏功率变异性的特征在于模型生成的分布,这些分布是使用蒙特卡洛分析获得的,并针对SPICE仿真进行了验证。提出的模型大约是700 泄漏功率变异性的特征在于模型生成的分布,这些分布是使用蒙特卡洛分析获得的,并针对SPICE仿真进行了验证。拟议的模型约为700 计算速度比SPICE仿真快,平均误差小于0.19%。

计算速度比SPICE仿真快,平均误差小于0.19%。

更新日期:2020-02-06

computationally faster than SPICE simulations with mean error being less than 0.19%.

computationally faster than SPICE simulations with mean error being less than 0.19%.

中文翻译:

考虑设备堆叠的亚阈值泄漏功率的过程诱导可变性建模

MOSFET的稳步降级为纳米级,已推动了电路设计中泄漏电流的支配,并已成为总IC功耗的重要组成部分。由于无法测量过程参数在其标称值附近的容忍度,这一问题进一步恶化。因此,改善静态功率预测的驱动力吸引了准确可靠的泄漏电流建模,特别是针对超低功耗应用。与门和带对隧道的泄漏相反,亚阈值泄漏对过程变化表现出很高的敏感性,因此已被考虑用于变化建模。器件电气和几何参数的波动导致亚阈值泄漏电流的分布更加广泛。因此,考虑到堆叠效应,提出了一种在阈值电压存在变化的情况下估计亚阈值电路中亚阈值泄漏功率的分析变异性模型。此外,结合栅极长度和宽度的同时变化,对阈值电压可变性对亚阈值泄漏功率的影响进行了建模。泄漏功率变异性的特征在于模型生成的分布,这些分布是使用蒙特卡洛分析获得的,并针对SPICE仿真进行了验证。拟议的模型约为700 泄漏功率变异性的特征在于模型生成的分布,这些分布是使用蒙特卡洛分析获得的,并针对SPICE仿真进行了验证。提出的模型大约是700 泄漏功率变异性的特征在于模型生成的分布,这些分布是使用蒙特卡洛分析获得的,并针对SPICE仿真进行了验证。拟议的模型约为700

计算速度比SPICE仿真快,平均误差小于0.19%。

计算速度比SPICE仿真快,平均误差小于0.19%。

京公网安备 11010802027423号

京公网安备 11010802027423号