当前位置:

X-MOL 学术

›

Int. J. Circ. Theory Appl.

›

论文详情

Our official English website, www.x-mol.net, welcomes your

feedback! (Note: you will need to create a separate account there.)

A high‐resolution all‐digital pulse‐width modulator architecture with a tunable delay element in CMOS

International Journal of Circuit Theory and Applications ( IF 1.8 ) Pub Date : 2020-04-27 , DOI: 10.1002/cta.2803 Juan Ignacio Morales 1 , Fernando Chierchie 1 , Pablo Sergio Mandolesi 1, 2 , Eduardo Emilio Paolini 1, 2

International Journal of Circuit Theory and Applications ( IF 1.8 ) Pub Date : 2020-04-27 , DOI: 10.1002/cta.2803 Juan Ignacio Morales 1 , Fernando Chierchie 1 , Pablo Sergio Mandolesi 1, 2 , Eduardo Emilio Paolini 1, 2

Affiliation

|

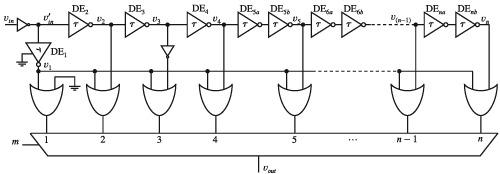

A design for an all‐digital high‐resolution pulse‐width modulator (HRPWM) architecture is presented in this work. The architecture is based on a novel digitally controlled delay element that combines two different approaches, achieving a variable time interval up to 54 ps, and adjustable against process, voltage, and temperature (PVT) variations. The proposed system uses several delay elements with a counter‐based digital pulse‐width modulator (DPWM) in a hybrid configuration, which allows to obtain duty cycles with 18‐bit resolution without using a high‐frequency internal clock and maintaining a low power dissipation.

中文翻译:

具有CMOS可调延迟元件的高分辨率全数字脉宽调制器架构

本文介绍了一种全数字高分辨率脉冲宽度调制器(HRPWM)架构的设计。该架构基于新颖的数控延迟元件,该元件结合了两种不同的方法,可实现高达54 ps的可变时间间隔,并可根据工艺,电压和温度(PVT)的变化进行调整。拟议的系统在混合配置中使用了几个延迟元件和基于计数器的数字脉宽调制器(DPWM),从而无需使用高频内部时钟即可保持18位分辨率的占空比,并保持低功耗。

更新日期:2020-04-27

中文翻译:

具有CMOS可调延迟元件的高分辨率全数字脉宽调制器架构

本文介绍了一种全数字高分辨率脉冲宽度调制器(HRPWM)架构的设计。该架构基于新颖的数控延迟元件,该元件结合了两种不同的方法,可实现高达54 ps的可变时间间隔,并可根据工艺,电压和温度(PVT)的变化进行调整。拟议的系统在混合配置中使用了几个延迟元件和基于计数器的数字脉宽调制器(DPWM),从而无需使用高频内部时钟即可保持18位分辨率的占空比,并保持低功耗。

京公网安备 11010802027423号

京公网安备 11010802027423号