当前位置:

X-MOL 学术

›

Adv. Electron. Mater.

›

论文详情

Our official English website, www.x-mol.net, welcomes your

feedback! (Note: you will need to create a separate account there.)

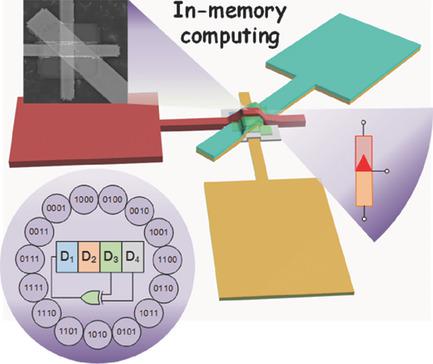

Boolean and Sequential Logic in a One‐Memristor‐One‐Resistor (1M1R) Structure for In‐Memory Computing

Advanced Electronic Materials ( IF 5.3 ) Pub Date : 2018-06-28 , DOI: 10.1002/aelm.201800229 Ya-Xiong Zhou,Yi Li,Nian Duan,Zhuo-Rui Wang,Ke Lu,Miao-Miao Jin,Long Cheng,Si-Yu Hu,Ting-Chang Chang,Hua-Jun Sun,Kan-Hao Xue,Xiang-Shui Miao

Advanced Electronic Materials ( IF 5.3 ) Pub Date : 2018-06-28 , DOI: 10.1002/aelm.201800229 Ya-Xiong Zhou,Yi Li,Nian Duan,Zhuo-Rui Wang,Ke Lu,Miao-Miao Jin,Long Cheng,Si-Yu Hu,Ting-Chang Chang,Hua-Jun Sun,Kan-Hao Xue,Xiang-Shui Miao

|

Memristive devices acting as high‐performance in‐memory computing fabrics have attracted much attention for nonvolatile parallel architectures to break the von Neumann bottleneck. Here, for the first time, a nonvolatile digital logic system with three‐terminal Pt/SiO2/Pt/Ag/GeTe/Ta one‐memristor‐one‐resistor (1M1R) structure is presented. Programmable nonvolatile Boolean logic gates and clocked sequential logic blocks including D latch and D flip‐flop are experimentally implemented, based on which a 4‐bit linear‐feedback shift register with timing design is functionally verified in simulation. With information generation, processing, transmission, and storage performing within the same 1M1R‐based logic blocks, these results consolidate the feasibility of building memristive digital computing system for future non‐von Neumann computing.

中文翻译:

用于存储器中计算的单忆阻一电阻(1M1R)结构中的布尔和顺序逻辑

用作高性能内存计算结构的忆阻设备已引起非易失性并行体系结构的突破,从而打破了冯·诺依曼瓶颈。在这里,首次提出了具有三端Pt / SiO 2 / Pt / Ag / GeTe / Ta单忆阻单电阻(1M1R)结构的非易失性数字逻辑系统。可编程非易失性布尔逻辑门和时钟时序逻辑块,包括D锁存器和D触发器是通过实验实现的,基于此,具有时序设计的4位线性反馈移位寄存器在仿真中得到了功能验证。通过在相同的基于1M1R的逻辑块中执行信息生成,处理,传输和存储,这些结果巩固了为未来的非冯·诺依曼计算构建忆阻数字计算系统的可行性。

更新日期:2018-06-28

中文翻译:

用于存储器中计算的单忆阻一电阻(1M1R)结构中的布尔和顺序逻辑

用作高性能内存计算结构的忆阻设备已引起非易失性并行体系结构的突破,从而打破了冯·诺依曼瓶颈。在这里,首次提出了具有三端Pt / SiO 2 / Pt / Ag / GeTe / Ta单忆阻单电阻(1M1R)结构的非易失性数字逻辑系统。可编程非易失性布尔逻辑门和时钟时序逻辑块,包括D锁存器和D触发器是通过实验实现的,基于此,具有时序设计的4位线性反馈移位寄存器在仿真中得到了功能验证。通过在相同的基于1M1R的逻辑块中执行信息生成,处理,传输和存储,这些结果巩固了为未来的非冯·诺依曼计算构建忆阻数字计算系统的可行性。

京公网安备 11010802027423号

京公网安备 11010802027423号