当前位置:

X-MOL 学术

›

Adv. Energy Mater.

›

论文详情

Our official English website, www.x-mol.net, welcomes your feedback! (Note: you will need to create a separate account there.)

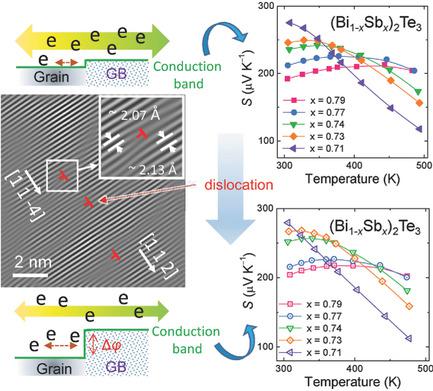

Effect of Dislocation Arrays at Grain Boundaries on Electronic Transport Properties of Bismuth Antimony Telluride: Unified Strategy for High Thermoelectric Performance

Advanced Energy Materials ( IF 27.8 ) Pub Date : 2018-04-06 , DOI: 10.1002/aenm.201800065 Jae-Yeol Hwang 1 , Jungwon Kim 2 , Hyun-Sik Kim 3 , Sang-Il Kim 4 , Kyu Hyoung Lee 5 , Sung Wng Kim 1

Advanced Energy Materials ( IF 27.8 ) Pub Date : 2018-04-06 , DOI: 10.1002/aenm.201800065 Jae-Yeol Hwang 1 , Jungwon Kim 2 , Hyun-Sik Kim 3 , Sang-Il Kim 4 , Kyu Hyoung Lee 5 , Sung Wng Kim 1

Affiliation

|

Taming electronic and thermal transport properties is the ultimate goal in the quest to achieve unprecedentedly high performance in thermoelectric (TE) materials. Most state‐of‐the‐art TE materials are inherently narrow bandgap semiconductors, which have an inevitable contribution from minority carriers, concurrently decreasing Seebeck coefficient and increasing thermal conductivity. Nevertheless, the restraint control of minority carrier transport is seldom considered as a key element to enhance the TE figure of merit (zT). Herein, it is verified that the localized dislocation arrays at grain boundaries enable the suppression of minority carrier contribution to electronic transport properties, resulting in an increase of the Seebeck coefficient and the carrier mobility in bismuth antimony tellurides. It is also suggested that the suppression of minority carriers via the generation of dislocation arrays at grain boundaries is an effective and noninvasive strategy to optimize overall electronic transport properties without sacrificing predominant characteristics of majority carriers in TE materials.

中文翻译:

晶界位错阵列对碲化铋锑电子输运性能的影响:高热电性能的统一策略

为了在热电(TE)材料中实现前所未有的高性能,驯服电子和热传输特性是最终目标。大多数最先进的TE材料本质上都是窄带隙半导体,少数载流子不可避免地会带来贡献,同时会降低塞贝克系数并增加热导率。然而,很少考虑限制少数载人运输是提高TE品质因数(zT)的关键因素。)。在此,证实了晶界处的局部位错阵列能够抑制少数载流子对电子传输性能的贡献,从而导致锡贝克系数和碲化铋锑中载流子迁移率的增加。还建议通过在晶界处生成位错阵列来抑制少数载流子是一种有效且无创的策略,可在不牺牲TE材料中多数载流子的主要特征的情况下优化整体电子传输性能。

更新日期:2018-04-06

中文翻译:

晶界位错阵列对碲化铋锑电子输运性能的影响:高热电性能的统一策略

为了在热电(TE)材料中实现前所未有的高性能,驯服电子和热传输特性是最终目标。大多数最先进的TE材料本质上都是窄带隙半导体,少数载流子不可避免地会带来贡献,同时会降低塞贝克系数并增加热导率。然而,很少考虑限制少数载人运输是提高TE品质因数(zT)的关键因素。)。在此,证实了晶界处的局部位错阵列能够抑制少数载流子对电子传输性能的贡献,从而导致锡贝克系数和碲化铋锑中载流子迁移率的增加。还建议通过在晶界处生成位错阵列来抑制少数载流子是一种有效且无创的策略,可在不牺牲TE材料中多数载流子的主要特征的情况下优化整体电子传输性能。

京公网安备 11010802027423号

京公网安备 11010802027423号