Abstract

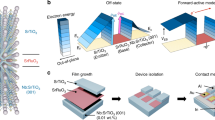

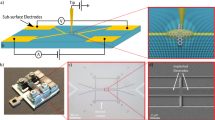

The miniaturization of silicon-based electronics has motivated considerable efforts in exploring new electronic materials, including two-dimensional semiconductors and halide perovskites, which are usually too delicate to maintain their intrinsic properties during the harsh device fabrication steps. Here we report a convenient plug-and-probe approach for one-step simultaneous van der Waals integration of high-k dielectrics and contacts to enable top-gated transistors with atomically clean and electronically sharp dielectric and contact interfaces. By applying the plug-and-probe top-gate transistor stacks on two-dimensional semiconductors, we demonstrate an ideal subthreshold swing of 60 mV per decade. Using this approach on delicate lead halide perovskite, we realize a high-k top-gate CsPbBr3 transistor with a low operating voltage and a very high two-terminal field-effect mobility of 32 cm2 V−1 s−1. This approach can be extended to centimetre-scale MoS2 and perovskite and generate top-gated transistor arrays, offering a rapid and convenient way of accessing intrinsic properties of delicate emerging materials.

This is a preview of subscription content, access via your institution

Access options

Access Nature and 54 other Nature Portfolio journals

Get Nature+, our best-value online-access subscription

$29.99 / 30 days

cancel any time

Subscribe to this journal

Receive 12 print issues and online access

$259.00 per year

only $21.58 per issue

Buy this article

- Purchase on Springer Link

- Instant access to full article PDF

Prices may be subject to local taxes which are calculated during checkout

Similar content being viewed by others

Data availability

The data that support the plots within this paper and other findings of this study are available from the corresponding author upon reasonable request.

References

Moore, G. E. Cramming more components onto integrated circuits, reprinted from Electronics, volume 38, number 8, April 19, 1965, pp. 114 ff. IEEE J. Solid-State Circuits 11, 33–35 (2006).

Meindl, J. D., Chen, Q. & Davis, J. A. Limits on silicon nanoelectronics for terascale integration. Science 293, 2044–2049 (2001).

International Roadmap for Devices and Systems (IEEE, 2021). https://irds.ieee.org/editions/2021

Sze, S. M. & Ng, K. K. Physics of Semiconductor Devices (2006).

Keyes, R. W. Fundamental limits of silicon technology. Proc. IEEE 89, 227–239 (2001).

Zhang, G. Q., Graef, M. & Roosmalen, F. V. The rationale and paradigm of ‘more than Moore’. In 56th Electronic Components and Technology Conference, pp. 151–157 (IEEE, 2006).

Fiori, G. et al. Electronics based on two-dimensional materials. Nat. Nanotechnol. 9, 768–779 (2014).

Liu, Y. et al. Promises and prospects of two-dimensional transistors. Nature 591, 43–53 (2021).

Nie, W. et al. High-efficiency solution-processed perovskite solar cells with millimeter-scale grains. Science 347, 522–525 (2015).

Cao, Y. et al. Perovskite light-emitting diodes based on spontaneously formed submicrometre-scale structures. Nature 562, 249–253 (2018).

Chhowalla, M., Jena, D. & Zhang, H. Two-dimensional semiconductors for transistors. Nat. Rev. Mater. 1, 16052 (2016).

Akinwande, D., Petrone, N. & Hone, J. Two-dimensional flexible nanoelectronics. Nat. Commun. 5, 5678 (2014).

Leijtens, T., Bush, K. A., Prasanna, R. & McGehee, M. D. Opportunities and challenges for tandem solar cells using metal halide perovskite semiconductors. Nat. Energy 3, 828–838 (2018).

Liu, X.-K. et al. Metal halide perovskites for light-emitting diodes. Nat. Mater. 20, 10–21 (2021).

Yumoto, G. et al. Strong spin–orbit coupling inducing Autler–Townes effect in lead halide perovskite nanocrystals. Nat. Commun. 12, 3026 (2021).

Kim, H. G. & Lee, H.-B.-R. Atomic layer deposition on 2D materials. Chem. Mater. 29, 3809–3826 (2017).

Illarionov, Y. Y. et al. Insulators for 2D nanoelectronics: the gap to bridge. Nat. Commun. 11, 3385 (2020).

Jeon, J. H., Jerng, S.-K., Akbar, K. & Chun, S.-H. Hydrophobic surface treatment and interrupted atomic layer deposition for highly resistive Al2O3 films on graphene. ACS Appl. Mater. Interfaces 8, 29637–29641 (2016).

Li, W. et al. Uniform and ultrathin high-κ gate dielectrics for two-dimensional electronic devices. Nat. Electron. 2, 563–571 (2019).

Sheng, Y. et al. Gate stack engineering in MoS2 field-effect transistor for reduced channel doping and hysteresis effect. Adv. Electron. Mater. 7, 2000395 (2021).

McDonnell, S. et al. HfO2 on MoS2 by atomic layer deposition: adsorption mechanisms and thickness scalability. ACS Nano 7, 10354–10361 (2013).

Xuan, Y. et al. Atomic-layer-deposited nanostructures for graphene-based nanoelectronics. Appl. Phys. Lett. 92, 013101 (2008).

Straus, D. B., Guo, S., Abeykoon, A. M. M. & Cava, R. J. Understanding the instability of the halide perovskite CsPbI3 through temperature-dependent structural analysis. Adv. Mater. 32, 2001069 (2020).

Senanayak Satyaprasad, P. et al. Understanding charge transport in lead iodide perovskite thin-film field-effect transistors. Sci. Adv. 3, e1601935 (2017).

Schulman, D. S., Arnold, A. J. & Das, S. Contact engineering for 2D materials and devices. Chem. Soc. Rev. 47, 3037–3058 (2018).

Haick, H., Niitsoo, O., Ghabboun, J. & Cahen, D. Electrical contacts to organic molecular films by metal evaporation: effect of contacting details. J. Phys. Chem. C 111, 2318–2329 (2007).

Liao, L. et al. High-κ oxide nanoribbons as gate dielectrics for high mobility top-gated graphene transistors. Proc. Natl Acad. Sci. USA 107, 6711 (2010).

Liu, Y. et al. Van der Waals heterostructures and devices. Nat. Rev. Mater. 1, 16042 (2016).

Liu, Y., Huang, Y. & Duan, X. Van der Waals integration before and beyond two-dimensional materials. Nature 567, 323–333 (2019).

Wang, P. & Duan, X. Probing and pushing the limit of emerging electronic materials via van der Waals integration. MRS Bull. 46, 534–546 (2021).

Lee, G.-H. et al. Flexible and transparent MoS2 field-effect transistors on hexagonal boron nitride–graphene heterostructures. ACS Nano 7, 7931–7936 (2013).

Illarionov, Y. Y. et al. Ultrathin calcium fluoride insulators for two-dimensional field-effect transistors. Nat. Electron. 2, 230–235 (2019).

Liao, L. et al. High-performance top-gated graphene-nanoribbon transistors using zirconium oxide nanowires as high-dielectric-constant gate dielectrics. Adv. Mater. 22, 1941–1945 (2010).

Liao, L. et al. Top-gated graphene nanoribbon transistors with ultrathin high-k dielectrics. Nano Lett. 10, 1917–1921 (2010).

Liao, L. et al. High-speed graphene transistors with a self-aligned nanowire gate. Nature 467, 305–308 (2010).

Cheng, R. et al. High-frequency self-aligned graphene transistors with transferred gate stacks. Proc. Natl Acad. Sci. USA 109, 11588 (2012).

Cheng, R. et al. Few-layer molybdenum disulfide transistors and circuits for high-speed flexible electronics. Nat. Commun. 5, 5143 (2014).

Liu, Y. et al. Toward barrier free contact to molybdenum disulfide using graphene electrodes. Nano Lett. 15, 3030–3034 (2015).

Liu, Y. et al. Approaching the Schottky–Mott limit in van der Waals metal–semiconductor junctions. Nature 557, 696–700 (2018).

Chen, P. et al. Approaching the intrinsic exciton physics limit in two-dimensional semiconductor diodes. Nature 599, 404–410 (2021).

Wang, J. et al. Transferred metal gate to 2D semiconductors for sub-1 V operation and near ideal subthreshold slope. Sci. Adv. 7: eabf8744.

Wang, Y. et al. Probing photoelectrical transport in lead halide perovskites with van der Waals contacts. Nat. Nanotechnol. 15, 768–775 (2020).

Manchanda, L. & Gurvitch, M. Yttrium oxide/silicon dioxide: a new dielectric structure for VLSI/ULSI circuits. IEEE Electron Device Lett. 9, 180–182 (1988).

Wang, Z. et al. Growth and performance of yttrium oxide as an ideal high-κ gate dielectric for carbon-based electronics. Nano Lett. 10, 2024–2030 (2010).

Durand, C. et al. Electrical property improvements of yttrium oxide-based metal–insulator–metal capacitors. J. Vac. Sci. Technol. A 24, 459–466 (2006).

Liu, H. & Ye, P. D. MoS2 dual-gate MOSFET with atomic-layer-deposited Al2O3 as top-gate dielectric. IEEE Electron Device Lett. 33, 546–548 (2012).

Radisavljevic, B., Radenovic, A., Brivio, J., Giacometti, V. & Kis, A. Single-layer MoS2 transistors. Nat. Nanotechnol. 6, 147–150 (2011).

Gurarslan, A. et al. Surface-energy-assisted perfect transfer of centimeter-scale monolayer and few-layer MoS2 films onto arbitrary substrates. ACS Nano 8, 11522–11528 (2014).

Li, T. et al. Epitaxial growth of wafer-scale molybdenum disulfide semiconductor single crystals on sapphire. Nat. Nanotechnol. 16, 1201–1207 (2021).

Acknowledgements

X.D. acknowledges financial support by the Office of Naval Research through grant number N00014-22-1-2631.

Author information

Authors and Affiliations

Contributions

X.D. conceived and led the project. P.W., L.W. and X.D. designed the experiments. L.W. and P.W. performed device fabrication, characterization and data analysis. J.H. participated in cross-section TEM characterization. B.P. performed the X-ray photoelectron spectroscopy measurements. C.J., Q.Q. and J.Z. prepared the materials. D.X. performed the ALD process. P.W., L.W., Y.H. and X.D. co-wrote the manuscript. All authors discussed the results and commented on the manuscript.

Corresponding author

Ethics declarations

Competing interests

The authors declare no competing interests.

Peer review

Peer review information

Nature Nanotechnology thanks Wenzhong Bao, Yang Chai and Tibor Grasser for their contribution to the peer review of this work.

Additional information

Publisher’s note Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Supplementary information

Supplementary Information

Supplementary Figs. 1–11, Tables 1 and 2 and references 1–22.

Rights and permissions

Springer Nature or its licensor holds exclusive rights to this article under a publishing agreement with the author(s) or other rightsholder(s); author self-archiving of the accepted manuscript version of this article is solely governed by the terms of such publishing agreement and applicable law.

About this article

Cite this article

Wang, L., Wang, P., Huang, J. et al. A general one-step plug-and-probe approach to top-gated transistors for rapidly probing delicate electronic materials. Nat. Nanotechnol. 17, 1206–1213 (2022). https://doi.org/10.1038/s41565-022-01221-1

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1038/s41565-022-01221-1

This article is cited by

-

Two-dimensional perovskite oxide as a photoactive high-κ gate dielectric

Nature Electronics (2024)

-

Wafer-scale and universal van der Waals metal semiconductor contact

Nature Communications (2023)

-

Two-dimensional materials-based integrated hardware

Science China Information Sciences (2023)