Abstract

Error-Tolerant applications regularly accomplish more data adaption. Approximate computing is one of the optimum strategies for data manipulation in several Error-Tolerant applications. It depletes circuit complexity and enhances area, power, and latency design parameters. Moreover, multiplication is a vital operation in Error-Tolerant applications. Existing Exact Multipliers are used in the approximate computing approach to expand the design parameters with fewer accuracy parameters in the present scenario. Hence, in this paper, new Rounding Based Static Segment Imprecise Multipliers (RBSSIM0, RBSSIM1) with and without Estimator Logic Circuit (ELC) are proposed to ameliorate the design and accuracy parameters. ELC removes lower-order important information in the input of bit length. Imprecise multiplication is executed using a rounding unit and barrel shifter in the proposed RBSSIM designs. These multipliers are synthesized and simulated using Cadence RTL compiler, Xilinx Vivado, and MATLAB with input bit sizes ranging from 8-bit to 32-bit. The results evidenced RBSSIM depletion area, delay, power, and energy by an average of 61.1%, 29.8%, 54.9%, and 64.2%, respectively, compared to existing imprecise multipliers. In addition to that, the proposed RBSSIM has better performance in terms of accuracy parameters. RBSSIM has improved NED, MRED, MED, and WCE on an average of 14.12%, 39.1%, 42.12%, and 24.21%, respectively. As a final point, RBSSIM provides higher SSIM and PSNR over the existing imprecise multipliers after including in the Error-Tolerant applications.

Similar content being viewed by others

Data Availability

Data sharing is irrelevant to this article since no data sets are generated or analyzed throughout the small proposed and existing Imprecise Multipliers.

References

Akbari O, Kamal M, Afzali-Kusha A, Pedram M (2018) CLA: A reconfigurable approximate carry look-ahead adder. IEEE Trans Circuits Syst II Express 65(8):1089–1093

Botella G, García C, Meyer-Bäse U (2013) Hardware implementation of machine vision systems: image and video processing. EURASIP J Adv Signal Process 152:1–4

Garg B, Patel S (2021) Reconfigurable rounding based approximate multiplier for energy efficient multimedia applications. Wireless Pers Commun 118(4):1–8

Garg B, Sharma G (2016) A quality-aware energy-scalable Gaussian smoothing filter for image processing applications. Microprocess Microsyst J 45:1–9

Garg B, Sharma G (2016) Low power signal processing via approximate multiplier for error-resilient applications. In Proc. of 11th International Conference on Industrial and Information Systems (ICIIS), IEEE, p 546–551

Garg B, Sharma G (2017) ACM: An energy-efficient accuracy configurable multiplier for error-resilient applications. J Electron Test 33(4):479–489

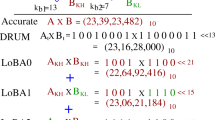

Garg B, Patel SK, Dutt S (2020) LoBA: a leading one bit based imprecise multiplier for efficient image processing. J Electron Test 36:429–437

Han J, Orshansky M (2013) Approximate computing: An emerging paradigm for energy-efficient design. In Proceeding of 18th IEEE European Test Symposium (ETS), IEEE European, p 1–6

Jothin R, Vasanthanayaki C (2018) High performance modified static segment approximate multiplier based on significance probability. J Electron Test 5:1–8

Kyaw KY, Goh W-L, Yeo K-S (2010) Low-power high-speed multiplier for error-tolerant application. In Proc. of IEEE International Conference of Electron Devices and Solid-State Circuits (EDSSC), IEEE, p 1–4

Kulkarni P, Gupta P, Ercegovac M (2011) Trading accuracy for power with an under designed multiplier architecture. In Proc. of 24th International Conference on VLSI Design, IEEE, p 346–351

Liang J, Han J, Lombardi F (2013) New metrics for the reliability of approximate and probabilistic adders. IEEE Trans Comp 62(9):1760–1771

Myler HR, Weeks AR (2009) The pocket handbook of image processing algorithms in C. Englewood Cliffs, NJ, and USA: Prentice-Hall

Strollo AGM, Napoli E, De Caro D, Petra N, Meo GD (2020) Comparison and extension of approximate 4–2 compressors for low-power approximate multipliers. IEEE Trans Circuits Syst I Regul Pap 67(9):3021–3034

Tilak Raju D, Srinivasa Rao Y (2021) Investigation of error-tolerant approximate multipliers for image processing applications. In Proc. of 3rd International Conference on Communication and Intelligent Systems (ICCIS 2021), Springer, p 1–14

Vahdat S, Kamal M, Afzali-Kusha A, Pedram M (2019) TOSAM: An energy-efficient truncation-and rounding-based scalable approximate multiplier. IEEE Trans Very Large Scale Integr VLSI Syst 27(5):1161–1173

Vasudevan M, Chakrabarti C (2014) Image processing using approximate Datapath units. In Proc. of IEEE International Symposium on Circuits and Systems (ISCAS), IEEE, p 1544–1547

Wang Z, Bovik A, Sheikh H, Simoncelli E (2004) Image quality assessment: from error visibility to structural similarity. IEEE Trans Image Process 13(4):600–612

Zendegani R, Kamal M, Bahadori M, Afzali-Kusha A, Pedram M (2017) RoBa multiplier: A rounding-based approximate multiplier for high-speed yet energy-efficient digital signal processing. IEEE Trans Very Large Scale Integr VLSI Syst 25(2):393–401

Author information

Authors and Affiliations

Corresponding author

Ethics declarations

Conflict of Interest

I certify no actual or potential conflict of interest about this article.

Competing Interests

The authors declare that they have no known competing financial interests or personal relationships that could influence the work reported in this paper.

Additional information

Responsible Editor: S. T. Chakradhar

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Raju, D.T., Rao, Y.S. Efficient Design of Rounding Based Static Segment Imprecise Multipliers for Error Tolerance Application. J Electron Test 38, 371–379 (2022). https://doi.org/10.1007/s10836-022-06011-0

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10836-022-06011-0