Abstract

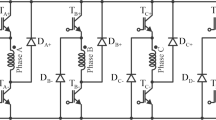

To enhance the reliability of converters, many fault-tolerant converters have been proposed in the literature. However, the design rule is seldom proposed. The converter is usually a switch circuit that can be described by the matrix; therefore, the design of a fault-tolerant converter can be transformed to the matrix design. The fault tolerance of a circuit is mainly determined by its alternative loops. In this study, minus-1 Boolean determinant is defined to establish a relationship between the matrix and the alternative loop. Then, the following proposition is proven: for a connection matrix of a circuit, the minus-1 Boolean determinant represents the sum of loops in the circuit, where each term of the minus-1 Boolean determinant represents a loop of the circuit. The asymmetric half bridge converter is the most commonly used converter of the switched reluctance motor (SRM). According to its connection matrix, its candidate fault-tolerant converters are listed, and with the proposition, their alternative loops are obtained, their fault tolerance performance is evaluated, and the optimal one is selected. Furthermore, the fault tolerance performance of the derived converter is tested by simulations and experiments on a 12/8 SRM.

Similar content being viewed by others

References

Kim, M.H., Lee, S., Lee, K.C.: Kalman predictive redundancy system for fault tolerance of safety-critical systems. IEEE Trans. Industr. Inform. 6(1), 46–53 (2010)

Muenchhof, M., Beck, M., Isermann, R.: Fault-tolerant actuators and drives-Structures, fault detection principles and applications. Annu. Rev. Control 42(8), 1294–1350 (2009)

Choi, U., Blaabjerg, F., Lee, K.: Study and handling methods of power IGBT module failures in power electronic converter systems. IEEE Trans. Power Electron. 30(5), 2517–2533 (2015)

Yang, S., Bryant, A., Mawby, P., et al.: An industry-based survey of reliability in power electronic converters. IEEE Trans. Ind. Appl. 47(3), 1441–1451 (2011)

Nallamekala, K.K., Sivakumar, K.: A fault-tolerant dual three-level inverter configuration for multipole induction motor drive with reduced torque ripple. IEEE Trans. Ind. Electron. 63(3), 1450–1457 (2016)

Zhao, N., Liu, J., Shi, Y., et al.: Mode analysis and fault-tolerant method of open-circuit fault for a dual active-bridge DC–DC converter. IEEE Trans. Ind. Electron. 67(8), 6916–6926 (2020)

Pires, V.F., Foito, D., Silva, J.F.: Fault-tolerant multilevel topology based on three-phase H-bridge inverters for open-end winding induction motor drives. IEEE Trans. Energy Convers. 32(3), 895–902 (2017)

Pires, V.F., Cordeiro, A., Foito, D., et al.: A multilevel fault-tolerant power converter for a switched reluctance machine drive. IEEE Access 8, 21917–21931 (2020)

Li, H., Li, W., Ren, H.: Fault-tolerant inverter for high-speed low-inductance BLDC drives in aerospace applications. IEEE Trans. Power Electron. 32(2), 2452–2463 (2017)

Salimian, H., Iman-Eini, H.: Fault-tolerant operation of three-phase cascaded H-bridge converters using an auxiliary module. IEEE Trans. Ind. Electron. 64(2), 1018–1027 (2017)

Cvetković, D.M., Doob, M., Sachs, H.: Spectra of graphs: theory and application, pp. 80–94. Academic Press, New York (1980)

Mayeda, W.: Graph theory, pp. 394–419. John Wiley, New York (1972)

Chen, W.K.: Applied graph theory. 141–203, pp. 141–203. Elsevier Science & Technology, Amsterdam (1976)

Adiga, C., Rakshith, B.R., So, W.: On the mixed adjacency matrix of a mixed graph. Linear Algebra Appl. 495, 223–241 (2016)

Moha, B.: A new kind of Hermitian matrices for digraphs. Linear Algebra Appl. 584, 343–352 (2020)

Ong, C.M., Liu, C.T., Lu, C.N.: Generation of connection matrices for digital simulation of converter circuits using the tensor approach. IEEE Trans. Power Syst. 2(4), 906–912 (1987)

Dorfler, F., Simpson-Porco, J.W., Bullo, F.: Electrical networks and algebraic graph theory: models, properties, and applications. Proc. IEEE 106(5), 977–1005 (2018)

Pollock, C., Williams, B.W.: Power converter circuits for switched reluctance motor with the minimum number of switches. IEEE Proc. B – Electr. Power Appl. 137(6), 373–384 (1990)

Ellabban O., Abu-Rub H.: Switched reluctance motor converter topologies: a review. In: Proceedings IEEE International Conference on Industrial Technology (ICIT), pp. 840–846 (2014). https://doi.org/10.1109/ICIT.2014.6895009

Pires, V.F., Pires, A.J., Cordeiro, A., Foito, D.: A review of the power converter interfaces for switched reluctance machines. Energies 13(13), 1–34 (2020)

Liang, Y., Chen, H., Shi, J., Liu, H.: New circuits for emulating switched reluctance motor windings. IET Electr. Power Appl. 10(6), 458–466 (2016)

Acknowledgements

This work is supported by the National Natural Science Foundation of China-NSFC-ASRT (Chinese-Egyptian) Cooperative Research Project under Grant No. 51961145401.

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Fang, C., Chen, H. Design rule for fault-tolerant converters of switched reluctance motors. J. Power Electron. 21, 1690–1700 (2021). https://doi.org/10.1007/s43236-021-00306-9

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s43236-021-00306-9