Abstract

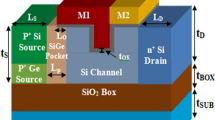

In recent technology, the demand for 3D multiple-gate MOSFETs such as FinFETs increase. In this paper, FinFETs are explored and reviewed. The scaling of planar MOSFET below 32nm technology increases the short channel effects (SCE). To improve the concert in low-power VLSI logic circuits and reduced the SCEs, we need enhanced gate controlling over the channel by using multigate technology. Here, we have discussed numerous architecture of FINFET, the threshold voltage (Vth) and supply voltage (Vdd) optimization, optimization of fin configuration, and low power technique for FinFET domino circuits.

Similar content being viewed by others

Data Availability

All sources of data are from reference cited in the paper.

References

Taur Y, Ning TH (1998) Fundamentals of modern VLSI Devices, 2nd edn. Cambridge Univ. Press, New York

Hu C (1996) IEEE Electron Devices Meeting, pp 319–322

Chen J, Chan TY, Chen IC, Ko PK, Hu C (1987) IEEE Electron Device Lett 8(11):515–517

Ghai D et al (2013) Circuits and Systems (MWSCAS). IEEE 56th International Midwest Symposium on, pp 809–812

Hisamoto D, Lee W-C, Kedzierski J et al (2000) IEEE Trans Electron Devices 47(12):2320–2325

Sairam T, Zhao W, Cao Y (2007) Optimizing FinFET technology for high-speed and low-power design. 17th Great Lakes Symposium on VLSI, pp 73–77

Hieda K et al (1987) IEDM Tech Dig, p 736

Hisamoto D et al (1989) IEDM Tech Dig, p 833

Yu B, Chang L, Ahmed S et al (2002) FinFET scaling to 10nm gate length. In: Proceedings of the IEEE International Devices Meeting (IEDM ‘02), pp 251–254, San Francisco, Calif, USA

Tang S, Chang L, Lindert N et al (2001) FinFET—a quasiplanar double-gate MOSFET. In: Proceedings of the International of Solid-State Circuits Conference, pp 118–119

Guillorn M, Chang J, Bryant A et al (2008) FinFET performance advantage at 22 nm: an AC Perspective. In: Proceedings of the Symposium on VLSI Technology Digest of Technical Papers (VLSIT ’08), pp 12–13

Yang FL, Lee D-H, Chen H-Y et al (2004) 5nm-gate nanowire FinFET,” in Proceedings of the Symposium on VLSI Technology-Digest of Technical Papers, pp 196–197

X.Huang W-C, Lee CKuo et al (1999) Sub 50-nm FinFET: PMOS. In: Proceedings of the IEEE International Devices Meeting (IEDM ‘99), pp 67–70, Washington, DC, USA

Nowak EJ, Aller I, Ludwig T et al (2004) Turning silicon on its edge [double gate CMOS/FinFET Technology]. IEEE Circuits Devices Mag 20(1):20–31

Collaert N, Demand M, Ferain I et al (2005) Tall triple-gate devices with TiN/HfO2 gate stack. Proc. of the Symposium on VLSI Technology, pp 108–109

Rainey B, Fried DM, Leong M, Kedzierski J, Nowak EJ (2002) Demonstration of FinFET CMOS circuit. 60th International Conference Digest Device Research Conference, pp 47–48

Lim H, Fossum JG (1983) Threshold voltage of thin-film silicon-on-insulator MOSFETs. IEEE Trans Electron Devices 30–10:1244

Lin CH, Chang J, Guillorn M, Bryant A, Oldiges P, Haensch W (2010) Non-planar device architecture for 15nm node: FinFET or trigate. In: Proceedings of the IEEE International Silicon on Insulator Conference (SOI ’10), pp 1–2

Anil KG, Henson K, Biesemans S, Collaert N (2003) Short-channel effect in fully-depleted SOI MOSFET’s. Proceedings of ESSDERC, 139

Takagi S, Toriumi A, Iwase M, Tango H (1994) On the Universality of Inversion Layer Mobility in Si MOSFET’s: Part II-Effects of Surface Orientation. IEEE Trans Electron Devices 41–12:2362

Sato T, Takeishi Y, Hara H (1969) Effects of crystal graphical orientation on mobility, surface state density and noise in p-type inversion layer on oxidized Si surfaces. Jpn J Appl Phys 8–5:588

Sato T, Takeishi Y, Hara H (1971) Mobility anisotropic of electron in inversion layers on oxidized silicon surfaces. Phys Rev B 4–6:1950

Yang M, Ieong M, Shi L, Chan K, Chan V, Chou A, Gusev E, Jenkins K, Boyd D, Ninomiya Y, Pendleton D, Surpris Y, Heenan D, Ott J, Guarini K, D’Emic C, Cobb M, Mooney P, To B, Rovedo N, Benedict J, Mo R, Ng H (2003) High performance CMOS fabricated on hybrid substrate with different crystal orientations. Technical Digest of IEDM, 18.7.1

Guillorn M et al (2008) FinFET performance advantage at 22nm: An AC perspective. Symp. VLSI Technol. Technical Digest, pp 12–13

C-Y.Kang et al (2013) Effect of layout and process parameter on device/circuit performance and variability for 10nm node FinFET technology. Symp. VLSI Technol. Technical Dig, pp 90–91

Colinge JP (2008) FinFETs and other multigate transistors. Springer, Berlin

Matsukawa T et al (2008) Dual metal gate FinFET integration by Ta/Mo diffusion technology for Vt reduction and multi-Vt CMOS application. https://doi.org/10.1109/ESSDERC.2008.4681753

Muralidhar R, Frank JC, Oldiges DJ, Lu P, Lauer DI (2013) Meeting the challenge of multiple threshold voltages in highly scaled undoped FinFETs. IEEE Trans Electron Devices 60(3):1276–1278

Ananthan H et al (2004) FinFET SRAM – Device and circuit design consideration. Quality Electronic Design, 2004. Proceedings 5th International Symposium, pp 511–516

Datta S et al (2013) Tunnel transistors for energy efficient computing. Reliability Physics Symposium (IRPS), 2013 IEEE International

Shuto Y et al (2013) FinFET-based pseudo-spin-transistor. Design and performance (ISCDG)

Ming-Hung, Han et al (2013) Device and circuit performance estimation of junctionless bulk FinFETs. IEEE Trans Electron Devices 60(6):1807–1813

Shaodi, Wang et al (2013) Evaluation of digital circuit-level variability in inversion-mode and junctionless FinFET technologies. IEEE Trans. Electron Devices 60(7):2186–2193

Garg S, Gupta TK (2019) FDSTDL: Low-power technique for FinFET domino circuits. Int J Circuit :1–24. https://doi.org/10.1002/cta.2627

Acknowledgements

The authors acknowledge the Microelectronics Computational Laboratory, Department of Electronics and Communication Engineering, National Institute of Technology Silchar, India for providing all necessary facilities to carry out the research work.

Funding

Young Faculty Research Fellowship scheme under Digital India Corporation.

Author information

Authors and Affiliations

Contributions

The first author has written and documented the paper and the second author collected the research material, checked, and modified the technical content.

Corresponding author

Ethics declarations

The work has maintained ethical standard.

Conflict of Interest

There is no conflict of interest.

Consent to Participate

The authors agree to participate.

Consent for Publication

The authors agree with the copyright policy of the journal.

Additional information

Publisher’s Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Maurya, R.K., Bhowmick, B. Review of FinFET Devices and Perspective on Circuit Design Challenges. Silicon 14, 5783–5791 (2022). https://doi.org/10.1007/s12633-021-01366-z

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s12633-021-01366-z