Abstract

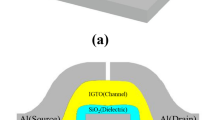

The gate material work function engineering and hetero-dielectric engineering concepts are discussed in this paper to design a novel triple material DG Tunnel FET. The three different work functions and the hetero-dielectric material within the transistor control the charge carrier density in the source, drain, and channel region. The heterojunction germanium and silicon material in the source-channel junction improve tunneling based on the bandgap engineering. The hetero-dielectric materials, namely high–K material in the source region and low-K material in the drain region, suppress the gate-to-drain capacitance effect, enhancing the cut-off frequency. The increased tunneling enhances the ON current, and the tri material restricts the reverse tunneling, which suppresses the ambipolar behaviour of the TFET. The electrical characteristics like surface potential, electric field, drain current, transconductance, and cut-off frequency of the TMDG TFET are simulated using TCAD simulation. Also, results validate the suitable selection of the doping concentration in the source, drain region and different tri-gate work function values for the proposed TMDG TFET. The proposed device shows remarkable progress in ON current of the order (10− 3 A/µm) and the leakage current in Femto range (10− 17 A/µm), with the ION/IOFF current ratio of 1014. The proposed structure is suitable for low-power applications.

Similar content being viewed by others

Data Availability

Not Applicable.

Code Availability

Not Applicable.

References

Choi WY, Lee W (2010) Hetero-gate-dielectric tunneling field-effect transistors. IEEE Trans Electron Devices 57(9):2317–2319

Sushree AS, Rupam G, Mohapatra SK (2019) Characteristics enhancement of hetero dielectric DG TFET using SiGe pocket at source/channel interface :Proposal and investigation. Silicon 12:513–520. Springer. https://doi.org/10.1007/s12633-019-00159-9

Sheeja H, Rani C, Bhoopathy Bagan K, Nirmal D, Solomon Roach R (2019) Enhancement of performance in TFET by reducing high-K dielectric length and drain electrode thickness. Silicon 12:2337–2343. Springer. https://doi.org/10.1007/s12633-019-00328-w

Sheeja H, Rani C, Bhoopathy Bagan K, Solomon Roach R (2020) Improved drain current characteristics of germanium source triple material double gate hetero-dielectric stacked TFET for low power applications. Silicon 13:2753–2762. Springer. https://doi.org/10.1007/s12633-020-00556-5

Kumar S, Ekta Goel K, Singh B, Singh P, Kumar K, Baral, Jit S (2017) 2-D Analytical modeling of the electrical characteristics of dual-material double-gate TFETs with a SiO2/HfO2 stacked gate-oxide structure. IEEE Trans Electron Devices 64(3):960–968

Kumar S, Singh K, Chander S, Goel E, Singh PK, Baral K, Singh B, Jit S (2018) 2D analytical drain current model of double-gate heterojunction TFETs with a SiO2/HfO2 stacked gate-oxide structure. IEEE Trans Electron Devices 65(1):331–338. https://doi.org/10.1109/TED.2017.2656630

Vimala P, Arun Samuel TS (2020) Investigation of cylindrical channel gate all around InGaAs/InP Heterojunction Heterodielectric tunnel FETs. Silicon (Springer). https://doi.org/10.1007/s12633-020-00691-z

Kumar SE, Goel K, Singh B, Singh MK, Jit S (2016) Compact 2-D analytical model for electrical characteristics of double–gate TFETs 63(8):3291–3299

Kumar M, Satyabrata J (2015) A novel four-terminal ferroelectric tunnel FET for quasi-ideal switch. IEEE Trans Nanotechnol 14(4):600–602. https://doi.org/10.1109/TNANO.2015.2427195

Ionescu AM, Heike R (2011) Tunnel field-effect transistors as energy efficient electronic switches. Nature 479:329–337. https://doi.org/10.1038/nature10679

Verhulst AS, Vandenberghe WG, Maex K, Groeseneken G (2007) Tunnel field-effect transistor without gate-drain overlap. Appl Phys Lett 91(5):053102

Verhulst AS, Bart Soree D, Leoneli, William G, Vandenberghe, Guido Groesenekan (2010) Modelling the single-gate,double-gate and gate-all around tunnel field effect transistor. J Appl Phys 107:1–8. https://doi.org/10.1063/1.3277044

Koester SJ, Lauer I, Majumdar A, Cai J, Sleight J, Bedell S, Solomon P, Laux S, Chang L, Koswatta S, Haensch W, Tomasini P, Thomas S (2010) Are Si/SiGe tunneling field-effect transistors a good idea? ECS Trans 33(6):357–361. https://doi.org/10.1149/1.3487566

Yu HS, Chui CO (2009) Insights and optimizations of tunnel field-effect transistor operation. IEEE Device Research Conference, pp 87–88

Bagga N, Sarkar SK (2015) An analytical model for tunnel barrier modulation in triple metal double gate TFET. IEEE Trans Electron Devices 62(7):2136–2142

Ahmad MS, Ahmad SA, Muqeem M, Alam N, Hasan M (2019) TFET-based robust 7T SRAM cell for low power application. IEEE Trans Electron Devices 66(9):334–3840

Sandow C, Knoch J, Urban C, Zhao QT, Mantl S (2009) Impact of electrostatics and doping concentration on the performance of silicon tunnel field-effect transistors. Solid-State Electron 53(10):1126–1131. https://doi.org/10.1016/j.sse.2009.05.009

Biswal SM, Baral B, DeD. Sarkar A (2016) Study of effect of gate length downscaling on the Analog/RF performance and Linearity Investigation of InAs-based nanowire Tunnel FET. Superlattice Microst 91(3):319–330

Mallik A, Chattopadhyay A (2012) Tunnel field effect transistors for analog /mixed –signal system-on-chip applications. IEEE Trans Electron Devices 59:888–894

Sedighi B, Hu X, Liu S, Nahas JJ, Niemier M (2015) Analog circuit design using tunnel –FETs. IEEE Trans Circuits Syst-I 62(1):39–48

Liu H, Li X, Vaddi R, Ma K, Datta S, Narayanan V (2014) Tunnel FET RF rectifier design for energy harvesting applications. IEEE J Emerg Sel Top Circuits Syst 14:400–411

Joshi T, Singh Y, Singh B (2020) Extended-source double-gate tunnel FET with improved DC and analog/RF performance. IEEE Trans Electron Devices 67(4):1873–1879

Acknowledgements

The author would like to thank Dr. L. Arivazhagan for interesting discussion on the device physics and simulation setup.

Author information

Authors and Affiliations

Contributions

Writing - literature search and analysis, original draft preparation: [C. Sheeja Herobin Rani] [R. Solomon Roach], Idea of the article, Resources [T. S. Arun Samuel], Checked the comparison results and validation: [S. Edwin Lawrence]

Corresponding author

Ethics declarations

Conflicts of Interest/competing Interests

The authors have no relevant financial or non-financial interests to disclose.

Ethics Approval and Consent to Participate

All authors freely agreed and gave their consent for the publication of this paper.

Consent for Publication

All authors freely agreed and gave their consent for the publication of this paper.

Additional information

Publisher’s Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Rani, C.S.H., Roach, R.S., Samuel, T.S.A. et al. Performance Analysis of Heterojunction and Hetero Dielectric Triple Material Double Gate TFET. Silicon 14, 5827–5834 (2022). https://doi.org/10.1007/s12633-021-01355-2

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s12633-021-01355-2