Abstract

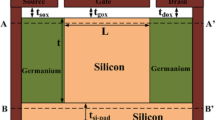

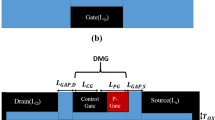

Our focus is on the need for novel devices and the careful investigation of an electrically doped III–V ternary alloy-based gate-all-around tunnel field effect transistor (GAA-TFET) and its circuit applicability. We explored the role of band gap engineering in analyzing GAA-TFET using lattice-matched GaPSb and InP in the source region and channel/drain regions, respectively. This enhances DC and analog characteristics. The device features were then extracted using Silvaco and imported into a Cadence Virtuoso environment using the Verilog-A method to design a sigma delta ADC. The ADC output was then filtered and decimation using MATLAB, resulting into an 11-bit data converter with a 71.24-dB signal to-noise ratio.

Similar content being viewed by others

References

J.S. Kilby, Chem. Phys. Chem. 2, 482 (2002).

A. Dixita, D.P. Samajdar, N. Bagga, and D.S. Yadav, Mater. Today Commun. 26, 101964 (2021)

S.G. Narenda, ACM J. Emerg. Technol. Comput. Syst. 1, 1 (2005)

J.T. Park and J.-P. Colinge, IEEE Trans. Electron Dev. 49, 12 (2002)

K. Boucart and A.M. Ionescu, IEEE Trans. Electron Dev. 54, 7 (2007)

S. Yadav, C. Rajan, D. Sharma, and S. Balotiya, in VLSI Design and Test. In: 23rd International Symposium, VDAT (2019), pp. 694–701.

C. Rajan, D. Sharma, and D.P. Samajdar, Superlattice Microst. 126, 72 (2019)

B.V. Chandan, K. Nigam, C. Rajan, and D. Sharma, J. Comput. Electron. 18, 4 (2019)

S. Yadav, D. Sharma, B.V. Chandan, M. Aslam, D. Soni, and N. Sharma, Superlattice Microst. 117, 9 (2018)

J. Patel, D. Sharma, S. Yadav, A. Lemtur, and P. Suman, Microelectron. J. 85, 72 (2019)

ATLAS Device Simulation Software, Silvaco Int (Santa Clara, CA, USA, 2014)

R. Gandhi, Z. Chen, N. Singh, and K. Banerjee, IEEE Electron Dev. Lett. 32, 4 (2011)

S. Adachi, III–V Ternary and Quaternary Compounds in Handbook of Electronic and Photonic Materials (Springer, Berlin, 2017)

A. Bhattacharjee, M. Saikiran, and S. Dasgupta, IEEE Trans. Electron Dev. 64, 10 (2017)

C. Rajan, D.P. Samajdar, J. Patel, A. Lodhi, S.K. Agnihotri, D. Sharma, and A. Kumar, J. Electron. Mater. 49, 7 (2020)

S. Pavan, R. Schreier, and G.C. Temes, Understanding Delta-Sigma Data Converters (Wiley, New York, 2017)

J. Candy, IEEE Trans. Commun. 34, 1 (1986)

A.Y. Kwentus, Z. Jiang, and A.N. Willson, IEEE Trans. Signal Process. 45, 2 (1997)

Author information

Authors and Affiliations

Corresponding author

Ethics declarations

Conflict of interest

The authors declare that they have no conflict of interest.

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Behera, A.K., Rajan, C., Samajdar, D.P. et al. Performance Analysis of Sigma Delta ADC Developed using Electrically Doped GAPSb/InP Gate All Around Tunnel Field Effect Transistor. J. Electron. Mater. 50, 5740–5753 (2021). https://doi.org/10.1007/s11664-021-09112-2

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s11664-021-09112-2