Abstract

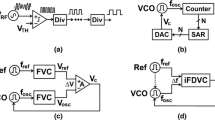

In this paper, an analytical model of a closed-loop frequency-locked loop (FLL) based on a two-stage voltage-controlled oscillator (VCO) is proposed. Switch capacitor technology is used to accelerate the conversion speed of the frequency-to-voltage converter for reducing the locking time. The VCO is reduced to the minimum two-stage delay ring structure for outputting high-frequency signals with less variation caused by process, voltage, and temperature drift. Based on the strategy that focuses on the optimization of the loop bandwidth, a low jitter GHz clock with a wide swing and a strong capacitive load driving ability is realized. The proposed FLL is implemented in TSMC 0.35 μm 3.3 V CMOS process. From the experimental results, the output frequency is ranged from 750 MHz to 1.27 GHz, and the RMS jitter of the output clock is less than 36 ps under 1.039 GHz. The generated low-jitter clock is suitable for GHz gating applications in single-photon detection.

Similar content being viewed by others

Data availability

The data of simulation and test results used to support the findings of this study are included within the article and have been deposited in the Figshare repository (https://doi.org/10.6084/m9.figshare.13225226).

References

W. Bae, H. Ju, K. Park, S. Cho, D. Jeong, A 7.6 mW, 214-fs RMS jitter 10-GHz phase-locked loop for 40-Gb/s serial link transmitter based on two-stage ring oscillator in 65-nm CMOS, in 2015 IEEE Asian Solid-State Circuits Conference (A-SSCC), Xiamen, China (2015), pp. 1–4. https://doi.org/10.1109/ASSCC.2015.7387448

H.T. Bui, Y. Savaria, Design of a high-speed differential frequency-to-voltage converter and its application in a 5-GHz frequency-locked loop. IEEE Trans. Circ. Syst. I Regul. Pap. 55(3), 766–774 (2008). https://doi.org/10.1109/TCSI.2008.916397

S. Cui, V. Acharya, B. Banerjee, A low-power and wide tuning range frequency locked loop for a Cognitive Radio system, in 2009 IEEE Radio and Wireless Symposium, San Diego, CA, USA (2009), pp. 364-367. https://doi.org/10.1109/RWS.2009.4957356

A. Djemouai, M.A. Sawan, M. Slamani, New frequency-locked loop based on CMOS frequency-to-voltage converter: design and implementation. IEEE Trans. Circ. Syst. II Analog Digit. Signal Process. 48(5), 441–449 (2001). https://doi.org/10.1109/82.938354

I. Ghorbel, F. Haddad, W. Rahajandraibe, M. Loulou, A subthreshold low-power CMOS LC-VCO with high immunity to PVT variations. Analog Integr. Circ. Signal Process. 93(3), 415–426 (2017). https://doi.org/10.1007/s10470-017-1047-7

H. Hwang, J. Kim, A 100Gb/s quad-lane serdes receiver with a PI-based quarter-rate all-digital CDR. Electronics 9(7), 1–16 (2020)

S. Jin, J. Chai, J. Li, A. Yan, 9 ps TDC based on multiple sampling in 0.18 μm complementary metal-oxide-semiconductor. ICE Circ. Dev. Syst. 14(4), 459–463 (2020). https://doi.org/10.1049/iet-cds.2019.0242

O. Jung, H. Seok, A. Dissanayake, S. Lee, A 45-μW, 162.1-dBc/Hz FoM, 490-MHz two-stage differential ring VCO without a cross-coupled latch. IEEE Trans. Circ. Syst. II Express Br. 65(11), 1579–1583 (2018). https://doi.org/10.1109/TCSII.2017.2766674

N. Kadayinti, A.J. Budkuley, M.S. Baghini, D.K. Sharma, Effect of jitter on the settling time of mesochronous clock retiming circuits. Analog Integr. Circ. Signal Process. 101(3), 623–640 (2019). https://doi.org/10.1007/s10470-018-1344-9

H. Liu, W. Rhee, Z. Wang, A 10.3 mW 13.6 GHz phase-locked loop with boosted Gm two-stage ring VCO, in 2016 13th IEEE International Conference on Solid-State and Integrated Circuit Technology (ICSICT), Hangzhou (2016), pp. 1443–1445. https://doi.org/10.1109/ICSICT.2016.7998763

M.S. McCorquodale et al., A 0.5-to-480 MHz self-referenced CMOS clock generator with 90 ppm total frequency error and spread-spectrum capability, in 2008 IEEE International Solid-State Circuits Conference - Digest of Technical Papers, San Francisco, CA, USA (2008), pp. 350–619. https://doi.org/10.1109/ISSCC.2008.4523201

K. Pappu, G. P. Reitsma, S. Bapat, Frequency-locked-loop ring oscillator with 3ns peak-to-peak accumulated jitter in 1ms time window for high-resolution frequency counting, in 2017 IEEE International Solid-State Circuits Conference (ISSCC), San Francisco, CA (2017), pp. 92–93. https://doi.org/10.1109/ISSCC.2017.7870276

Y. Shih, B. Otis, An on-chip tunable frequency generator for crystal-less low-power WBAN radio. IEEE Trans. Circ. Syst. II Express Br. 60(4), 187–191 (2013). https://doi.org/10.1109/TCSII.2013.2251938

K. Ueno, T. Asai, Y. Amemiya, A 30-MHz, 90-ppm/°C fully-integrated clock reference generator with frequency-locked loop, in 2009 Proceedings of ESSCIRC, Athens, Greece (2009), pp. 392–395. https://doi.org/10.1109/ESSCIRC.2009.5325940

Vinogradov, E. Popova, Status and perspectives of solid state photon detectors, Nuclear Instruments and Methods in Physics Research Section A: Accelerators, Spectrometers, Detectors and Associated Equipment. Volume 952, 2020, 161752, ISSN 0168-9002, https://doi.org/10.1016/j.nima.2018.12.067

C. Yan, J. Wu, C. Hu, X. Ji, A low power wide tuning range two stage ring VCO with frequency enhancing, in IEICE Electronics Express, 2019, Volume 16, Issue 8, Pages 20190090, Released April 25, 2019, ISSN 1349-2543.

M. Yang, Xu. Feihu, J.-G. Ren, J. Yin, Y. Li, Y. Cao, Qi. Shen, H.-L. Yong, L. Zhang, S.-K. Liao, J.-W. Pan, C.-Z. Peng, Spaceborne, low-noise, single-photon detection for satellite-based quantum communications. Opt. Express 27, 36114–36128 (2019)

D. Zheng, Z. Liu, X.-P. Yu, K. Huang, Design and optimization of CMOS glitch-free frequency-to-voltage converter for frequency-locked loop at GHz ranges. Analog Integr. Circ. Signal Process. 98(3), 627–632 (2019)

W. Zou, D. Ren, X. Zou, A wideband low-jitter PLL with an optimized Ring-VCO, in IEICE Electronics Express, 2020, Volume 17, Issue 3, Pages 20190703, Released February 10, 2020, [Advance publication] Released January 09, 2020, Online ISSN 1349-2543

Acknowledgments

This work was supported by Jiangsu Provincial Natural Science Fund (BK20181139), National Natural Science Foundation of China (No. 61805036), Science and Technology on Analog Integrated Circuit Laboratory Fund (JCKY2019210C030).

Author information

Authors and Affiliations

Corresponding author

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Wu, J., Sun, X., Zhou, M. et al. Modeling and Analysis of a Frequency-Locked Loop Based on Two-Stage Ring Voltage-Controlled Oscillator. Circuits Syst Signal Process 40, 5182–5203 (2021). https://doi.org/10.1007/s00034-021-01694-w

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s00034-021-01694-w