Abstract

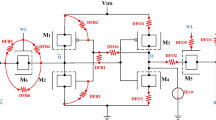

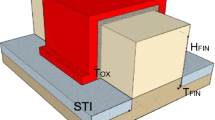

FinFET technology is used in leading high-performance/power-efficient electronic products. This technology has proven its efficiency after 22nm technology nodes. However, FinFET technology has new manufacturing and design complexities. Thus, it is required to study the behavior of defects in FinFET-based SRAM memories and develop new test strategies for those not covered by conventional test strategies based on CMOS fault modeling. This paper study open-gate defects affecting only one of the parallel fins in the driver transistors of the memory cell. These opens do not cause a functional fault but reduce the Static Noise Margin (SNM) of the memory cells. Moreover, they may fail under certain operating conditions and may constitute a long-term reliability issue. The behavior of these defects is studied for the hold, read and write operations using realistic defect models. By using a short write time test, the detection of these defects is investigated. The effectiveness of the short write time test method at nominal parameters and under process variations is evaluated. The detection probability of these defects can be further enhanced using a higher power supply voltage.

Similar content being viewed by others

Notes

Minimum write time is defined as the minimum required time to write both logic states correctly at the memory cell.

References

(2012) Itrs 2012 executive summary, ITRS.[Online]. Available: http://www.itrs.net

Bhoj AN, Simsir MO, Jha NK (2012) Fault models for logic circuits in the multigate era. IEEE Trans Nanotechnol 11(1):182–193

Chen MC, Wu TH, Wu CW (2018) A built-in self-test scheme for detecting defects in finfet-based sram circuit, in IEEE 27th Asian Test Symposium. IEEE, pp. 19–24

Dunga MV, Lin CH, Xi X, Lu DD, Niknejad AM, Hu C (2006) Modeling advanced fet technology in a compact model. IEEE Trans Electron Devices 53(9):1971–1978

Forero F, Villacorta H, Renovell M, Champac V (2019) Modeling and detectability of full open gate defects in finfet technology, IEEE Transactions on Very Large Scale Integration (VLSI) Systems 127(9)2180–2190

Guo D, et al (2014) 10nm finfet technology for low power and high performance applications, in 12th IEEE International Conference on Solid-State and Integrated Circuit Technology (ICSICT). IEEE

Hamdioui S, Taouil M, Haron NZ (2015) Testing open defects in memristor-based memories. IEEE Trans Comput 64(1):247–259

Harutyunyan G, Tshagharyan G, Vardanian V, Zorian Y (2014) IEEE 32nd VLSI Test Symposium (VTS). IEEE 2014:1–6

Harutyunyan G, Tshagharyan G, Zorian Y (2015) Impact of parameter variations on finfet faults, in IEEE 33rd VLSI Test Symposium (VTS). IEEE

Harutyunyan G, Tshagharyan G, Zorian Y (2015) Test and repair methodology for finfet-based memories. IEEE Trans Device Mater Reliab 15(1):3–9

Ichihashi M, Woo Y, Parihar S (2016) International Symposium on VLSI Technology, Systems and Application (VLSI-TSA). IEEE 2016:1–2

Kleeberger VB, Graeb H, Schlichtmann U (2013) Predicting future product performance: modeling and evaluation of standard cells in finfet technologies, in Proceedings of the 50th Annual Design Automation Conference. ACM, p. 33

Lin Y, Yu B, Xu B, Pan DZ (2017) Triple patterning aware detailed placement toward zero cross-row middle-of-line conflict. IEEE Trans Comput Aided Des Integr Circuits Syst 36(7):1140–1152

Liu Y, Xu Q (2012) IEEE International Test Conference. IEEE 2012:1–9

Lu DD, Lin CH, Niknejad AM, Hu C (2010) Compact modeling of variation in finfet sram cells. IEEE Design Test Comp 2(27):44–50

Medeiros G, Taouil M, Fieback M, Poehls L, Hamdioui S (2019) Dft scheme for hard-to-detect faults in finfet srams, in European Test Symposium. IEEE

Medeiros GC, Fieback M, Wu L, Taouil M, Poehls LMB, Hamdioui S (2021) Hard-to-detect fault analysis in finfet srams, IEEE Transactions on Very Large Scale Integration (VLSI) Systems. https://doi.org/10.1109/TVLSI.2021.3071940

Moreno J, Renovell M, Champac V (2016) Effectiveness of low-voltage testing to detect interconnect open defects under process variations, IEEE Transactions on Very Large Scale Integration (VLSI) Systems 24(1):378-382

Natarajan S, et al (2014) A 14nm logic technology featuring 2nd-generation finfet, air-gapped interconnects, self-aligned double patterning and a 0.0588 \(\mu m^2\) sram cell size, in IEEE International Electron Devices Meeting (IEDM). IEEE

Papoulis A, Pillai SU (2002) Probability, random variables, and stochastic processes. Tata McGraw-Hill Education

Patel K, Liu TJK, Spanos CJ (2009) Gate line edge roughness model for estimation of finfet performance variability. IEEE Trans Electron Devices 56(12):3055–3063

Predictive technology models, in Available: ptm.asu.edu

Pavlov A, Sachdev M, Jose PDG (2004) An sram weak cell fault model and dft technique with a programmable detection threshold, in2004IEEE International Test Conference. IEEE 2004:1006–1015

Wang X, Cheng B, Brown AR, Millar C, Asenov A (2012) Statistical variability in 14-nm node SOI finFETs and its impact on corresponding 6T-SRAM cell design. In Proceedings of the European Solid-State Device Research Conference (ESSDERC). IEEE, 2012, pp. 113–116

Weste NH, Harris DM (2011) Cmos Vlsi Design: A Circuits And Systems Perspective, 4/E. Pearson Education Inc

Author information

Authors and Affiliations

Corresponding author

Additional information

Responsible Editor: L. M. Bolzani Pöhls

Publisher’s Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Champac, V., Mesalles, J., Villacorta, H. et al. Analysis and Detection of Open-gate Defects in Redundant Structures of a FinFET SRAM Cell. J Electron Test 37, 369–382 (2021). https://doi.org/10.1007/s10836-021-05955-z

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10836-021-05955-z