Abstract

\(\varDelta \varSigma \) analog-to-digital converters (ADCs) are largely used in sensor acquisition applications. In the last few years, standalone \(\varDelta \varSigma \) modulators have become increasingly available as off-the-shelf parts. To build a complete ADC, a standalone modulator has to be paired with some advanced elaboration unit, such as a field programmable gate array (FPGA) or a digital signal processor (DSP), which is needed for the implementation of the decimation filter. This work investigates the use of low-cost, general-purpose microcontrollers for the decimation of \(\varDelta \varSigma \)-modulated signals. The main challenge is given by the clock frequency of the modulator, which can be in the range of a few \(\hbox {MHz}\). The proposed technique deals with this limitation by employing two serial peripheral interface (SPI) modules in a time-interleaved configuration. This approach allows for continuous acquisition and elaboration of relatively high-speed, digital signals. The technique has been applied to a case study, and a data conversion system has been practically realized. The performance of the proposed filter is compared to that of a digital filter, present on board a commercial microcontroller, and the results of experimental tests are provided.

Similar content being viewed by others

1 Introduction

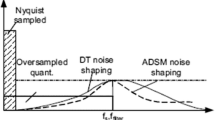

Data converters based on the \(\varDelta \varSigma \) modulation are widely used to digitize small-amplitude, low-frequency signals generated by sensors [3, 5, 6, 12]. One of the main requirements in these applications is a large dynamic range. \(\varDelta \varSigma \) converters represent a very good choice since they can achieve high resolution, at the expense of reduced signal bandwidth. A typical sensor acquisition chain can be represented by the block diagram in Fig. 1. The signal generated by the sensor is acquired by the ADC, and a digital signal is generated at its output. The digital code is further elaborated by a processing unit, typically for purposes of monitoring or control. \(\varDelta \varSigma \) converters operate in an oversampling regime and make use of the quantization noise shaping in order to achieve high resolution. The converter consists of two main sub-blocks, which are the modulator and the digital filter, also called decimator [13] [7], as shown in Fig. 1. The modulator has the task of sensing the analogue signal at the input and generating a digital representation at its output. It employs a low-resolution ADC, which frequently has only one bit resolution, to digitize the input quantity.

At the output of the modulator, a low-resolution, high-speed digital signal, containing information on the input quantity and shaped quantization noise, is present. In order for this signal to become a good representation of the input one, some elaboration is needed. The digital filter is the block which operates on the low-resolution digital signal and produces a high-resolution output code. The main task of the filter is that of removing the shaped quantization noise outside the signal band and converting the serial signal into a pulse code modulation (PCM) word at the output. The frequency response of the filter is such that the out-of-band quantization noise is attenuated while the in band signal is not affected. The other task of the filter is that of decimating the resulting samples. Since the input signal is oversampled, the data rate at the output of the filter would be unnecessarily large. The filter selectively drops output samples so that a data rate close to the Nyquist frequency is achieved. The reduced throughput makes it possible for the reduction of the requirements on the elaboration speed for the following circuitry, which might be a microcontroller unit (MCU), while preventing information loss. Since \(\varDelta \varSigma \) converters consist of two clearly distinguishable sub-blocks, the decimation filter can be built on-chip, close to the modulator or it can be built off-chip. An off-chip decimation filter is attractive for a few reasons. Firstly, the \(\varDelta \varSigma \) chip is much smaller and the power consumption is reduced. Secondly, an off-chip implementation can be more flexible if built by means of programmable devices, which allow for easy variation of the filter parameters. Thirdly, the communication between the modulator and the decimator only needs three wires in case of single-bit modulation; hence, it allows for an easy introduction of isolation barriers or power-domain translation. Digital signal processing can be performed directly on the high-speed bitstream—output signal of the \(\varDelta \varSigma \) modulator—by means of circuits implemented on FPGAs [9, 10]. However, these components are not as common as MCUs, which are readily available in almost every application where some kind of digital control is needed. So, a solution making use of a low-cost microcontroller, which does not have dedicated filtering hardware, as an alternative to the most expensive aforementioned solutions, might be worth investigating. Although digital filtering by means of software routines is very common, it typically operates on the signal at the Nyquist frequency [4] or, when the signal at the oversampling frequency is operated on, the clock frequency is limited to a few tens of \(\hbox {kHz}\) [2], while current-generation commercial modulators operate at clock frequencies of several \(\hbox {MHz}\). The main goal of this work is to present an approach to the decimation of \(\varDelta \varSigma \)-modulated signals, by using a low-cost, general-purpose microcontroller with no filtering-specific hardware. The proposed filtering technique relies on the use of two SPI modules in an interleaved configuration. This technique allows for continuous operation at clock frequencies up to several \(\hbox {MHz}\). The technique is described in detail in Sect. 2. A brief overview of the standard system architecture is presented in this section as well. The application of the technique to a case study is presented in Sect. 3. A practical realization of the proposed filter has been carried out, and the experimental results are presented in Sect. 4. Finally, in Sect. 5, conclusions are drawn.

2 System Architecture Description

2.1 Standard System Architecture Overview

In the last few years, \(\varDelta \varSigma \) modulators have become increasingly available as off-the-shelf parts [1]. Their main uses are in voltage, current and temperature sensing in industrial applications, as well as generic data-acquisition systems with high signal-to-noise ratio (SNR). The modulator presents a serial interface with one wire for the clock signal and one wire for the digital data signal. Since the output bitstream acquisition has to be synchronous, both the modulator and the digital filter operate with the same clock signal. Depending on the capabilities of the hardware used for implementing the filter, the clock can be provided by the device dedicated to the filtering, or it could be generated by an oscillator, which could be present inside some modulator chips. In both cases, the typical operation is that of sampling the signal on the non-active clock edge, so that a stable level is acquired (Fig. 2).

(a) Typical \(\varDelta \varSigma \) ADC architecture, with digital filter implemented on an FPGA or a DSP. The bidirectional arrow indicates that the clock can be generated by either the modulator chip or by the filtering module, depending on the available hardware. (b) Modulator data timing example. Data are generated on the falling edge and should be sampled on the rising edge of the clock signal

The digital signal elaboration can be performed by means of an FPGA, DSP or some high-performance MCU for implementing the decimation filter. These kind of platforms allow for synchronous acquisition and elaboration at clock frequencies of several \(\hbox {MHz}\), thanks to the presence of hardware components dedicated to the digital filtering: FPGAs are able to implement digital configurable circuits, while DSPs can exploit hardware adders and multipliers operating at high clock frequencies, for performing the digital filtering. The filtering can also be performed by means of configurable hardware filter peripherals, which are increasingly present inside last generation microcontrollers [14].

2.2 Motivation

As seen in 2.1, the standard architecture for building a data acquisition system based on a standalone \(\varDelta \varSigma \) modulator makes use of an FPGA or DSP for the implementation of the decimation filter. However, these kind of devices are not as commonly used as general-purpose microcontrollers in typical applications in which an elaboration unit acquires information from several sensors and drives several actuators. This work is motivated by the need of performing the decimation of \(\varDelta \varSigma \)-modulated signals without making use of expensive components such as FPGAs. This need arises in all those practical situations where a standalone \(\varDelta \varSigma \) modulator is the most suitable choice for the acquisition of the signal and a low-cost microcontroller is already available in the application. To the best of the authors’ knowledge, this issue has not been dealt with in previously published works. The proposed approach allows for the building of a data acquisition chain by means of low-cost components. At the same time, this approach guarantees high flexibility since it operates on the noise-shaped digital signal without any assumptions on the nature of the device generating the digital signal: it could be generated, for instance, by a \(\varDelta \varSigma \) modulator of an arbitrary order or by some sensor whose output is a pulse density modulation (PDM) signal. The choice of using an external modulator instead of the internal ADC of the microcontroller could be dictated by accuracy constraints. So, the proposed technique provides with the possibility of building an extremely flexible acquisition chain for decimating \(\varDelta \varSigma \)-modulated signals by making use of low-cost microcontrollers.

2.3 Proposed Elaboration Architecture

The main goal of this work is to present a method for continuous filtering of \(\varDelta \varSigma \)-modulated signals, by means of a low-cost microcontroller. While DSP or FPGA implementations are able to easily acquire high-speed digital signals synchronous to a clock signal, the same is not true for low-cost, general-purpose microcontrollers, where reading synchronous digital signals in the \(\hbox {MHz}\) range, on the general-purpose input–output (GPIO) pins, and processing them is not feasible. The proposed technique deals with this issue by using the SPI module of the microcontroller for the synchronous acquisition of the output signal of the modulator. The basic idea is that of acquiring a certain number of bits from the modulator by using the SPI module. After data acquisition, the central processing unit (CPU) can perform the filtering operations on the stored data. Since a continuous operation mode is desirable, a second SPI module performs the acquisition of another burst of bits while the CPU operates on the data. In Fig. 3, a representation of the blocks of interest inside a generic microcontroller is shown. For each SPI block only the clock (CLK) and Master In Slave Out (MISO) signals are shown since the Master Out Slave In (MOSI) and Slave Select (SS) signals are not used.

The signal acquisition occurs as follows: one of the two SPI modules generates the clock signal for the modulator and stores the incoming bits inside a buffer in Data RAM, exploiting its direct memory access (DMA) capabilities. At the end of the acquisition, the SPI module generates an END signal which has a double purpose: it acts as an interrupt signal for the CPU so that the calculation routine can start, and secondly, it acts as a START signal for a second SPI module which begins the acquisition of a second burst of data, as the CPU processes the data acquired by the first SPI module. The sequence of operations is presented by means of the timing diagram in Fig. 4. Performing the data acquisition at the same frequency as the clock of the modulator ensures that data are correctly sampled and stored, while the elaboration phase can be done at the CPU speed.

It is important to notice that this approach is virtually independent of the specific filter that is to be implemented; the only constraint is that the elaboration phase must take a time which is shorter than the time required for the acquisition of the data burst.

3 Case Study—CIC Filter

3.1 Filter Design

A decimation filter is taken as a case study, in order to demonstrate the practical implementation of the proposed technique. The considered filter is the cascaded integrator comb (CIC) described in [8], which has a sinc-type frequency response. It is important to notice that the filter to be implemented could be of any type, as long as the time required for the calculations is smaller than the time needed for the acquisition of one data burst. Indeed, the acquisition technique would be exactly the same; only the calculation routine would be different, depending on the chosen filter to be implemented. The choice of the CIC filter type is dictated by its popularity and ease of implementation. A sinc filter of order k has the following transfer function

where the order k determines the roll-off of the envelope, while the parameter R is related to the position of the transfer function nulls. When designing a decimation filter for a \(\varDelta \varSigma \) modulator, k is chosen equal to L+1, L being the order of the modulator [13]. R instead is chosen equal to the oversampling ratio so that the noise around the output data rate, which folds into baseband, is attenuated by the filter’s response. The implemented filter is a third-order CIC, which is suitable for decimating a second-order noise-shaped signal [13] that can be generated by a \(\varDelta \varSigma \) modulator or by a sensor, which directly produces a PDM signal. The choice of the order of the filter is related to the fact that the vast majority of the commercial standalone \(\varDelta \varSigma \) modulators have a second-order loop filter. The 3\(\hbox {dB}\) cutoff frequency is

for a third-order sinc filter, where \(f_{\mathrm {DR}}\) is the output data rate.

A simple block diagram representing (1) is shown in Fig. 6, with both the integrating and the comb sections operating at the higher clock frequency. The data-rate change is performed at the output of the filter by means of a downsampling operation. An alternative well-known implementation, presented in [8], moves the downsampling operation before the comb section, as shown in Fig. 7. In this case, the differential delay is unity, so the memory requirements for the comb section are reduced, while the overall transfer function remains the same. Another advantage is that the comb section operates at the lower clock rate in this case. This kind of structure can be built without the use of multipliers; hence, it is very economical in terms of computation capability requirements.

3.2 Software Implementation

The software implementation of the filter is straightforward and follows from the diagram in Fig. 7. The flow chart of the filtering algorithm is shown in Fig. 8.

The intermediate variables of the filter are defined as 32-bit integers. This is done after considering the register growth as presented in [8]. The length of the burst is fixed at 128 bits, which is equal to the decimation rate. The 128 bits are stored in memory as 4 contiguous bytes. By looking at the block diagram of the filter shown in Fig. 7, it can be understood that, for each burst, the integrative (accumulative) action is performed for each incoming bit, while the derivative action is performed only once at the end, since the derivative part of the filter operates at the lower clock frequency. At the end of each elaboration cycle, the output word is shifted in order to account for the register growth [8] and it is truncated to the desired number of bits, which is 16 in this case.

4 Experimental Results

4.1 Test Setup

In this section, the results of the experimental tests are presented. An off-the-shelf second-order \(\varDelta \varSigma \) modulator [1] is used to generate the signal to be processed. The filter is implemented on board a low-cost, general-purpose microcontroller [11]. The clock signal for the modulator is generated by the OR operation between the clock signals of the two SPI modules, while the data signal is fed to the MISO input of both SPI modules, as shown in the lower branch in Fig. 9. The SPI master clocks the modulator at 4 \(\hbox {MHz}\) and reads the data on the rising edge of the clock signal, since the chosen modulator generates data on the falling edge of the clock. A hardware filtering module, which is present on board a commercial microcontroller [14], is also employed for comparison purposes. The choice of the filtering module to be used for the comparison is dictated by the popularity of such a device, in conjunction with a second-order \(\varDelta \varSigma \) modulator, in power metering applications. The filter module can be configured so that it has the same parameters as the proposed filter, namely third-order sinc response with a decimation rate equal to 128. The chosen filter parameters yield an output data rate of

and a 3 \(\hbox {dB}\) cutoff frequency of

The test bench is represented in Fig. 9: a sinusoidal signal is fed to two acquisition chains. Both chains include an anti-aliasing filter and a second-order \(\varDelta \varSigma \) modulator. The anti-aliasing filter is a first-order RC with pole frequency at 91.5 \(\hbox {kHz}\), approximately one decade larger than the bandwidth of the digital filter. The two modulators are identical in order for the digital data stream to be ideally the same in both branches. The upper modulator is clocked by the hardware digital filter module, while the lower one is clocked by the microcontroller implementing the proposed technique. The two output bitstreams are then processed by the two decimation filters, and the resulting samples are sent to a PC through a serial interface, for further elaboration.

The sine wave at the input of the modulators has 250 \(\hbox {mV}\) amplitude, equal to the modulator full range, so that the SNR is maximized. Measurements at several frequencies of the input signal are taken, in order to validate the operation of the filter, and dynamic figures such as SNR, signal-to-noise and distortion ratio (SINAD) and spurious-free dynamic range (SFDR) are computed on a data record of 8192 samples.

4.2 Measurement Results

Measurements at different frequencies were taken in order to verify the operation of the system in the passband. The time-domain representation of a 800 \(\hbox {Hz}\) sinusoid, filtered with both techniques, is shown in Fig. 10. Spectral analysis was performed on the two data sets, by means of the fast Fourier transform (FFT) in order to assess the noise properties of the resulting signal. The input signal frequency was not locked to the clock frequency; hence, the data were windowed with a Blackman window in order to reduce the spectral leakage. The two spectra are shown in Fig. 11, and the input signal component can be clearly seen at 800 \(\hbox {Hz}\) with an amplitude of 0 \(\hbox {dBFS}\). The visible harmonics are mainly due to the input signal source; hence, they have approximately the same amplitude in both cases. The noise floor level is similar for the two cases as well. All measurement results are shown in Table 1.

It can be seen that the proposed software filtering technique achieves a better performance than the hardware digital filter. The lower performance of the hardware filter is to be attributed to the widening of the main lobe, as the noise floor is virtually the same for both filters. The SNR versus frequency, for both filtering techniques, is shown in Fig. 12. For the proposed filter, the droop in the frequency response can be clearly seen, as the frequency of the input signal is increased. Close to the cutoff frequency, the SNR drops by approximately 3\(\hbox {dB}\) with respect to the value in passband, which is in perfect agreement with the theoretical frequency response of the CIC filter.

5 Conclusion

A technique for the acquisitions and elaboration of \(\varDelta \varSigma \) modulators has been presented. The proposed approach makes use of a low-cost microcontroller, which does not contain any specific filtering dedicated hardware, but it relies on the use of two SPI modules in a time-interleaved configuration. The proposed technique requires the use of four pins of the microcontroller instead of only two, which is a factor to be considered if the number of pins of the microcontroller is a critical parameter in the project. The application of the proposed technique has been illustrated by means of the software implementation of a CIC decimation filter. By using an off-the-shelf second-order \(\varDelta \varSigma \) modulator clocked at 4 \(\hbox {MHz}\), a SINAD of approximately 79 \(\hbox {dB}\) (which corresponds to 12.8 ENOB) is achieved in a bandwidth of 15.625 \(\hbox {kHz}\). The 3 \(\hbox {dB}\) bandwidth of the CIC filter with decimation ratio of 128 is at 8.19 \(\hbox {kHz}\). The performance of the filter has been compared to that of a hardware filtering module having the same characteristics. The limitation in the clock frequency is given by the time that is required for the filtering operations, which has to be shorter than the acquisition time, which, in turn, depends on the complexity of the filtering algorithm and on the computational performance of the microcontroller.

Data Availability

The datasets generated during and/or analysed during the current study are available from the corresponding author on reasonable request.

References

zADuM7701, Datasheet. https://www.analog.com/en/products/adum7701.html

B. Ando, A. Cocuccio, S. Graziani and M. Lo Presti, A /spl Sigma//spl Delta/ A/D converter realized by using ST52X440 microcontroller. In Proceedings of the 21st IEEE Instrumentation and Measurement Technology Conference (IEEE Cat. No.04CH37510), pp. 553–556 Vol. 1. (2004). https://doi.org/10.1109/IMTC.2004.1351109

S. Brigati, F. Francesconi, P. Malcovati and F. Maloberti, A fourth-order single-bit switched-capacitor /spl Sigma/-/spl Delta/ modulator for distributed sensor applications. In IEEE Transactions on Instrumentation and Measurement, vol. 53, no. 2, pp. 266–270, (2004). https://doi.org/10.1109/TIM.2003.822480

N. T. Bui et al., Real-time filtering and ecg signal processing based on dual-core digital signal controller system. In IEEE Sensors Journal, vol. 20, no. 12, pp. 6492–6503, 15 (2020). https://doi.org/10.1109/JSEN.2020.2975006.

Y. Choi, H. Kim, H. Roh and J. Roh, A 290-\({\mu }\)W 25-kHz continuous-time delta-sigma modulator for acoustic sensor networks. 2009 IEEE 8th International Conference on ASIC, pp. 447–450, (2009). https://doi.org/10.1109/ASICON.2009.5351278.

E. Dallago, P. Malcovati, D. Miatton, T. Ungaretti, G. Venchi, Analysis of sigma-delta converters for MEMS sensors using power supply voltage as reference. IEE Proc. Circuits Dev. Syst. 153(5), 473–479 (2006). https://doi.org/10.1049/ip-cds:20060079

J.M. de la Rosa, Sigma-Delta Converters: Practical Design Guide (Wiley, Hoboken, 2019)

E. Hogenauer, An economical class of digital filters for decimation and interpolation,” in IEEE Transactions on Acoustics, Speech, and Signal Processing, vol. 29, no. 2, pp. 155–162, (1981). https://doi.org/10.1109/TASSP.1981.1163535

Y. Lim, Y. Yu, H. Zheng et al., FPGA implementation of digital filters synthesized using the FRM technique. Circuits Syst. Signal Process. 22, 211–218 (2003). https://doi.org/10.1007/s00034-004-7027-z

I.D.S. Miranda, A.C.C. Lima, An FPGA-oriented FFT algorithm for sigma-delta signals. Circuits Syst. Signal Process 39, 2459–2472 (2020)

nRF52832, Datasheet. https://www.nordicsemi.com/en/Products/Low%20power%20short-range%20wireless/nRF52832/Getting%20started

S. Pan and K. A. A. Makinwa, A 0.25 \(mm^2\)-Resistor-Based Temperature Sensor With an Inaccuracy of 0.12 \(^\circ \text{C}\) (3 \(\sigma \) ) From -55 \(^\circ \text{ C }\) to 125 \(^\circ \text{ C }\). In IEEE J. Solid-State Circuits, vol. 53, no. 12, pp. 3347–3355, (2018). https://doi.org/10.1109/JSSC.2018.2869595.

S. Pavan, R. Schreier, G.C. Temes, Understanding Delta-Sigma Data Converters (Wiley, Hoboken, 2017)

STM32H745, Datasheet. https://www.st.com/en/microcontrollers-microprocessors/stm32h745-755.html

Funding

Open access funding provided by Politecnico di Torino within the CRUI-CARE Agreement.

Author information

Authors and Affiliations

Corresponding author

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

This work was partially supported by the Power Electronics Innovation Center (PEIC), Politecnico di Torino, Italy. (Corresponding author: Markeljan Fishta)

Rights and permissions

Open Access This article is licensed under a Creative Commons Attribution 4.0 International License, which permits use, sharing, adaptation, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons licence, and indicate if changes were made. The images or other third party material in this article are included in the article’s Creative Commons licence, unless indicated otherwise in a credit line to the material. If material is not included in the article’s Creative Commons licence and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder. To view a copy of this licence, visit http://creativecommons.org/licenses/by/4.0/.

About this article

Cite this article

Fishta, M., Fiori, F. Decimation of Delta-Sigma-Modulated Signals Using a Low-Cost Microcontroller. Circuits Syst Signal Process 40, 6387–6400 (2021). https://doi.org/10.1007/s00034-021-01772-z

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s00034-021-01772-z