Abstract

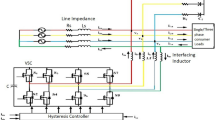

The control algorithm of a DSTATCOM majorly influences its function. The key role of a phase locked loop (PLL) as a fundamental extractor in the control algorithm is inevitable. It is used to extract the information of the fundamental like phase angle, frequency and amplitude from the distorted voltage/current signal. According to the information collected, the performance of the control algorithm of the DSTATCOM is judged for various conditions like unbalanced and distorted harmonic condition. This paper presents the study of three PLLs, namely unified three-phase signal processor PLL (UTSP), multi-sequence harmonic decoupling PLL (MSHDC) and harmonic/inter-harmonic DC offset (HIHDO) PLL. An unconstrained optimization problem has been formulated with DC and AC bus voltage errors. The gains of proportional integral controller are projected using RAO algorithm. It is an algorithm specific type and parameter less. The DSTATCOM is able to compensate the reactive power and mitigate the grid current harmonics which are caused due to a nonlinear load through an optimized PI controller for the considered PLL the control algorithms. An analysis of performance using simulation results, dynamic response and complexity in computation has been made for the PLLs considered. The fast recovery during dynamic conditions of the system has opted HIHDO PLL as better one among the other two proposed PLLs. The laboratory performance of the considered system for HIHDO PLL using d-SPACE has been provided.

Similar content being viewed by others

References

George JW (2007) Power system harmonics: fundamental, analysis, and filter design. Springer, New York

Barker PP, Burke JJ, Mancao RT, Short TA, Warren CA, Bums CW, Siewierski JJ (1994) Power quality monitoring of a distribution system. IEEE Trans Power Deliv 9(2):1136–1142

Moreno Munoz A (2007) Power quality: mitigation technologies in a distributed environment. Springer, London

Singh B, Chandraand A, Al-Haddad K (2014) Power quality: problems and mitigation techniques. Wiley, New York

Tey LH, So PL, Chu YC (2005) Improvement of power quality using adaptive shunt active filter. IEEE Trans Power Deliv 20(2):1558–1568

Acha JE, Agelidis YG, Anaya Lara O, Miller TEJ (2002) Power electronics control in electrical system. Newnes power engineering series, Woburn

Benysek G (2007) Improvement in the quality of delivery of electrical energy using power electronics. Springer, London

Ahmad S, Potdar MS (2019) Real and reactive power compensation of a power system by using DSTATCOM. In: 2nd International conference on signal processing and communication (ICSPC), Coimbatore, India, pp 148–152

Mariun N, Alam A, Mahmod S, Hizam H (2004) Review of control strategies for power quality conditioners. In: Proceedings of national power and energy conference, Kuala Lunipur, pp 109–115.

IEEE Recommended Practices and requirement for Harmonic Control on Electric Power System, IEEE Std.519, 1992

Ghosh A, Ledwich G (2009) Power quality enhancement using custom power devices. Springer, Delhi

Massoud AM, Finney SJ, Williams BW (2004) Review of harmonic current extraction techniques for an active power filter. In: Proceedings of 11th international conference on harmonics and quality of power, pp 154–159

Sao CK, Lehn PW, Iravani MR, Martinez JA (2002) A bench mark system for digital time domain simulation of a pulse width modulated DSTATCOM. IEEE Trans Power Deliv 17(4):1113–1120

Ranjan A, Kewat S, Singh B (2019) DSOGI-PLL based solar grid interfaced system for alleviating power quality problems. National power electronics conference (NPEC), Tiruchirappalli, India, pp 1–6

Zanchetta P, Sumner M, Marinelli M, Cupertino F (2009) Experimental modelling and control design of shunt active power filters. J Control Eng Pract 17:1126–1135

Kaura V, Blasko V (1997) Operation of a phase locked loop system under distorted utility conditions. IEEE Trans Ind Appl 33(1):58–63

Hsich GC, Hung J (1996) Phase locked loop system under distorted utility conditions. IEEE TRANS IND Electron 43:609–615

Golestan S, Guerrero JM, Vasquez JC (2017) Three-phase PLLs: a review of recent advances. IEEE Trans Power Electron 32(3):1894–1907

Silva SM, Lopes BM, Cardoso BJ, Campana RP, Boaventura WC (2004) Performance Evaluation of PLL algorithms for single phase grid connected systems. In: Proceedings of the IEEE industrial applications annual meeting IAS 04, vol 4, pp 2259–2263

Guo X, Wu W, Gu H (2011) Phase locked loop and synchronization methods for grid interfaced converters: a review. J Electric Rev 87(4):182–187

Jaalam N, Rahim NA, Bakar AHA, Tan C, Haider AMA (2016) A comprehensive review of synchronization methods for grid connected converters of renewable energy source. J Renew Sustain Energy Rev 59:1471–1481

Komarska T, Janik D, Peroutka Z (2013) Synchronization of grid connected converters for single phase systems. In: IEEE proceedings on European conference on power electronics and applications, pp 1–8

Karimi H, Seyedi Y, Ghartemani MK (2019) A robust and simple phase locked loop for unbalanced power grid applications. In: Proceedings of 28th international symposium on industrial electronics (ISIE 2019), vol 19, pp 29–34

Hadjidemetriou L, Kyriakides E, Blaabjerg F (2013) Synchronization of grid connected renewable energy sources under highly distorted voltages and unbalanced grid faults. in: proceedings of 39th annual conference of the IEEE industrial electronics society (IECON 2013), vol 9, pp 1887–1892

Ali Z, Christopher N, Hadjidemetriou L, Kyriakides E (2018) Design of an advanced PLL for accurate phase angle extraction under grid voltage HIH and DC offset. IET Power Electron 11:995–1008

Du KL, Swamy MNS (2010) Search and optimization by meta heuristics. Birkhauser, Canada

Rao RV (2020) Rao algorithms: three metaphor less simple algorithms for solving optimization problems. Int J Ind Eng Comput 11:107–130

Funding

Under Science and Engineering Research Board-New Delhi Project (Extra Mural Research Funding Scheme), Grant No. SB/S3/EECE/030/2016, DATED 17/08/2016.

Author information

Authors and Affiliations

Corresponding author

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Appendices

Appendix 1

1.1 Parameters for simulation work

400 V 50 Hz Three-phase AC supply, 0.06 Ω source resistance, 1mH source inductance, an AC voltage controller type nonlinear load (R = 10 Ω and L = 2mH and R = 45 Ω and L = 2mH during unbalance in one phase) DC bus voltage 700 V, 10 micro sec of sampling time, Interfacing inductance (Lf) = 2.25 mH, switching frequency (fs) = 5 kHz, cut-off frequency of low-pass filter = 10 Hz.

Appendix 2

2.1 Parameters for test work

AC mains: 3-phase, 230 V (line) with distortion, 50 Hz; nonlinear-type load: AC voltage controller with restive load (R = 21 Ω and R = 45 Ω during unbalance in ‘A’ phase) ohm; passive filter parameter (ripple filter): Rf = 5 Ω, Cf = 20μF; sampling time (Ts) = 40 μs, DC bus voltage = 400 V; DC bus capacitor (Cdc) = 4500 μF; interfacing inductor: Lf = 4 mH, DC bus cut-off frequency of low-pass filter = 10 Hz.

Rights and permissions

About this article

Cite this article

Arya, S.R., Maurya, R., Srikakolapu, J. et al. Compensation of power quality problems through DSTATCOM using various phase locked loops. Electr Eng 104, 45–66 (2022). https://doi.org/10.1007/s00202-021-01341-2

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s00202-021-01341-2