Abstract

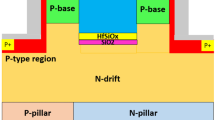

We propose a novel deep gate lateral double diffused metal-oxide-semiconductor (LDMOS) field-effect transistor in partial silicon-on-insulator (PSOI) technology for achieving high breakdown voltage and reduced power dissipation. In the proposed device, an N+ well is inserted in the buried oxide under the drain region. By optimizing the N+ well and the lateral distance between the buried oxide and the left side of the device, the electric field is modified. Therefore, the breakdown voltage improves. Also, the PSOI technology used in the proposed structure has a significant effect on reducing the lattice temperature. Our simulation results show that the proposed structure improves the breakdown voltage by about 67.5% and reduces the specific on-resistance by about 20% in comparison with a conventional LDMOS.

Similar content being viewed by others

References

Dong, Z., Duan, B., Fu, C., Guo, H., Cao, Z., Yang, Y.: Novel LDMOS optimizing lateral and vertical electric field to improve breakdown voltage by multi-ring technology. IEEE Electron. Device Lett. 39(9), 1358–1361 (2018). https://doi.org/10.1109/LED.2018.2854417

Erlbacher, T.: Lateral power transistors in integrated circuits. Springer, Berlin (2014)

Mehrad, M., Zareiee, M., Orouji, A.A., Member, S.: Controlled kink effect in a novel high-voltage ldmos transistor by creating local minimum in energy band diagram. IEEE Trans. Electron. Device 64(10), 4213–4218 (2017)

Shokouhi Shoormasti, A., Abbasi, A., Orouji, A.A.: Improvement the breakdown voltage and the on-resistance in the LDMOSFET: double buried metal layers structure. Silicon (2020). https://doi.org/10.1007/s12633-020-00684-y

Saadat, A., Put, M., Edwards, H., Vandenberghe, W.G.: Channel length optimization for planar ldmos field-effect transistors for low-voltage. IEEE J. Electron. Dev. Soc. 8, 711–715 (2020)

Anvarifard, M.K.: An impressive structure containing triple trenches for RF power performance (TT-SOI-MESFET). J. Comput. Electron. 17(1), 230–237 (2017)

Anvarifard, M.K.: Superlattices and microstructures symmetrical SOI MESFET with a dual cavity region (DCR-SOI MESFET) to promote high-voltage and radio-frequency performances. Superlattices Microstruct. 98, 492–503 (2016)

Anvarifard, M.K.: Creation of a new high voltage device with capable of enhancing driving current and breakdown voltage. Mater. Sci. Semicond. Process. 60, 60–65 (2017)

Jamali Mahabadi, S.E., Rajabi, S., Loiacono, J.: A novel partial SOI LDMOSFET with periodic buried oxide for breakdown voltage and self heating effect enhancement. Superlattices Microstruct. 85(2015), 872–879 (2015)

Tahne, B.A., Naderi, A., Heirani, F.: Reduction in self-heating effect of SOI MOSFETs by three vertical 4H-SiC layers in the BOX. Silicon 12(4), 975–986 (2020)

Mansoori, H.A., Orouji, A.A., Dideban, A.: New technique to extend the vertical depletion region at SOI-LDMOSFETs. J. Comput. Electron. 16(3), 666–675 (2017)

Hong, J.H., Chung, S.K., Choi, Y.I.: Optimum design for minimum on-resistance of low voltage trench power MOSFET. Microelectron. J. 35(3), 287–289 (2004)

Singh, Y., Rawat, R.S.: High figure-of-merit SOI power LDMOS for power integrated circuits. Eng. Sci. Technol. Int. J. 18(2), 141–149 (2015)

Appels, J.A, Vaes, H.M.J.: High voltage thin layer devices (Resurf Devices). Adv. Chem. Ser. 238–242 (1979). https://doi.org/10.1109/IEDM.1979.189589

Weibe, J., Matthus, C., Schlichting, H., Mitlehner, H., Erlbacher, T.: RESURF n-LDMOS transistor for advanced integrated circuits in 4H-SiC. IEEE Trans. Electron. Device 67(8), 3278–3284 (2020)

Orouji, A.A., Sharbati, S., Fathipour, M.: A new partial-SOI LDMOSFET with modified electric field for breakdown voltage improvement. IEEE Trans. Device Mater. Reliab. 9(3), 449–453 (2009)

Orouji, A.A., Mahabadi, S.E.J., Keshavarzi, P.: Superlattices and microstructures a novel partial SOI LDMOSFET with a trench and buried P layer for breakdown voltage improvement. Superlattices Microstruct. 50(5), 449–460 (2011)

Orouji, A.A., Moghadam, H.A., Dideban, A.: Double window partial SOI- LDMOSFET: a novel device for breakdown voltage improvement. Phys. E Low-Dimens. Syst. Nanostruct. 43(1), 498–502 (2010)

Mehrad, M., Orouji, A.A., Taheri, M.: Materials Science in semiconductor processing A new technique in LDMOS transistors to improve the breakdown voltage and the lattice temperature. Mater. Sci. Semicond. Process. 34, 276–280 (2015)

Device Simulator ATLAS, Silvaco, International (2012)

Cristoloveanu, S.: Silicon on insulator technologies and devices: from present to future. Solid State Electron. 45, 1403–1411 (2001)

Hu, Y.U.E., Liu, H., Xu, Q., Wang, L., Wang, J., Member, S.C.: Dimension effect on breakdown voltage of partial SOI LDMOS. IEEE J. Electron. Devices Soc. 5(3), 157–163 (2017)

Hu, Y., et al.: A high-voltage (>600 V) N-Island LDMOS with step-doped drift region in partial SOI technology. IEEE Trans. Electron. Devices 63(5), 1969–1976 (2016)

Inada, M., Yagi, S., Yamamoto, Y., Piao, G., Shimizu, M., Okumura ,H., Arai, K.: Low specific on-resistance AlGaN/GaN HEMT on sapphire substrate. In: Proceeding of the IEEE International Symposium on Power Semiconductor Devices IC’s (ISPSD), pp. 1–4 (2006). https://doi.org/10.1109/ISPSD.2006.1666085

Orouji, A.A., Pak, A.: Numerical simulation of lateral diffused metal oxide semiconductor field effect transistors: a novel technique for electric field control to improve breakdown voltage. Mater. Sci. Semicond. Process. 34, 230–235 (2015)

Pak, A., Orouji, A.A.: A novel technique at LDMOSs to improve the figure of merit. Superlattices Microstruct. 93, 11–17 (2016)

Gavoshani, A., Orouji, A.A., Abbasi, A.: A novel deep gate LDMOS structure using double P-trench to improve the breakdown voltage and the on-state resistance. Silicon, 1–6 (2021). https://doi.org/10.1007/s12633-020-00857-9

Author information

Authors and Affiliations

Corresponding author

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Gavoshani, A., Orouji, A.A. A novel deep gate power MOSFET in partial SOI technology for achieving high breakdown voltage and low lattice temperature. J Comput Electron 20, 1513–1519 (2021). https://doi.org/10.1007/s10825-021-01724-5

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10825-021-01724-5