Abstract

This article presents a high-performance hybrid full adder (HPHFA) designed with static CMOS logic and pass transistor logic to achieve better power delay product (PDP). The circuit was implemented using cadence virtuoso tool on gpdk 90 nm and 45 nm CMOS process technologies. Further, the structure has been extended to 32 bits to test the performance of HPHFA in higher-order circuitry. The proposed design was compared with popular conventional adders based on power consumption, delay and PDP. The proposed adder cell achieves 5.08–70.50% and 6.31–48.03% improvement in speed and power consumption, respectively, in 45 nm when compared to other conventional full adders (FAs). Also, the proposed design exhibits robustness against process variation and noise immunity with better driving capability.

Similar content being viewed by others

Data Availability Statement

The authors declare that the data supporting the findings and obtained during this research work are available within the paper.

References

M. Aguirre-Hernandez, M. Linares-Aranda, CMOS full-adders for energy-efficient arithmetic applications. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 19(4), 718–721 (2011)

M. Alioto, G. Di Cataldo, G. Palumbo, Mixed full adder topologies for high-performance low-power arithmetic circuits. Microelectron. J. 38(1), 130–139 (2007)

P. Bhattacharyya, B. Kundu, S. Ghosh, V. Kumar, A. Dandapat, Performance analysis of a low-power high-speed hybrid 1-bit full adder circuit. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 23(10), 2001–2008 (2015)

H .T. Bui, Y. Wang, Y. Jiang, Design and analysis of low-power 10-transistor full adders using novel XOR-XNOR gates. IEEE Trans. Circuits Syst. II, Analog Digit. Signal Process. 49(1), 25–30 (2002)

C .H. Chang, J .M. Gu, M. Zhang, A review of 0.18-\(\mu \)m full adder performances for tree structured arithmetic circuits. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 13(6), 686–695 (2005)

W.C. Elmore, The transient response of damped linear networks with particular regard to wideband amplifiers. J. Appl. Phys. 19(1), 55–63 (1948)

S. Goel, A. Kumar, M.A. Bayoumi, Design of robust, energy-efficient full adders for deep-submicrometer design using hybrid-CMOS logic style. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 14(12), 1309–1321 (2006)

I. Hassoune, D. Flandre, I. O’Connor, J. Legat, ULPFA: a new efficient design of a power-aware full adder. IEEE Trans. Circuits Syst. I Regul. Pap. 57(8), 2066–2074 (2010)

P. Kumar, R.K. Sharma, An energy efficient logic approach to implement CMOS full adder. J. Circuits Syst. Comput. 26(5), 1–20 (2017)

R.F. Mirzaee, M.H. Moaiyeri, H. Khorsand, K. Navi, A new robust and hybrid high-performance full adder cell. J. Circuits Syst. Comput. 20(4), 641–655 (2011)

H. Naseri, S. Timarchi, Low-power and fast full adder by exploring new XOR and XNOR gates. IEEE Trans. Very Large Scale Integr. (VLSI) Syst., 26(8), 1481–1493 (2018)

K. Navi, M. Maeen, V. foroutan, S. Timarchi, O. Kavehei, A novel low-power full-adder cell for low voltage. VLSI J. Integr. 42(4), 457–467 (2009)

M.C. Parameshwara, H.C. Srinivasaiah, Low-power hybrid 1-bit full adder circuit for energy efficient arithmetic applications. J. Circuits Syst. Comput. 26(1), 1–15 (2017)

J.M. Rababey, A. Chandrakasan, B. Nikolic, Digital Integrated Circuits: A Design Perspective, 2nd edn. (Pearson Education, Delhi, 2003)

D. Radhakrishnan, Low-voltage low-power CMOS full adder. IEE Proc. Circuits Devices Syst. 148(1), 19–24 (2001)

A .M. Shams, T .K. Darwish, M .A. Bayoumi, Performance analysis of low-power 1-bit CMOS full adder cells. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 10(1), 20–29 (2002)

C. K. Tung, Y. C. Hung, S. H. Shieh and G. S. Huang, A low-power high-speed hybrid CMOS full adder for embedded system, in Proceedings of IEEE Conference Design Diagnostics Electronic Circuits System, vol. 13, pp. 1–4 (2007)

L. Wang, N.R. Shanbhag, Noise-tolerant dynamic circuit design, in Proceedings of IEEE International Symposium on Circuits and Systems (ISCAS), vol. 1 (Orlando, FL, 1999), pp. 549–552

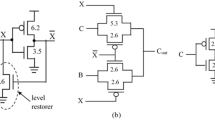

M. Zhang, J. Gu, and C.-H. Chang, A Novel hybrid pass logic with static CMOS output drive full adder cell, in Proceedings of International Symposium on Circuits and Systems, pp. 317–320 (2003)

R. Zimmermann, W. Fichtner, Low-power logic styles: CMOS versus pass-transistor logic. IEEE J. Solid-State Circuits 32(7), 1079–1090 (1997)

Author information

Authors and Affiliations

Corresponding author

Ethics declarations

Conflict of interest

The authors declare that they have no conflict of interest.

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Rajagopal, T., Chakrapani, A. A Novel High-Performance Hybrid Full Adder for VLSI Circuits. Circuits Syst Signal Process 40, 5718–5732 (2021). https://doi.org/10.1007/s00034-021-01725-6

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s00034-021-01725-6