Abstract

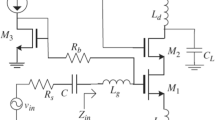

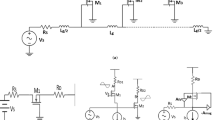

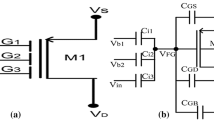

This paper presents a CMOS low power Variable Gain Low Noise Amplifier for 26–34 GHz in 45 nm process technology, which composes of cascaded complimentary common gate (CCG) stage and digital current steering amplifier. First stage is CCG stage, which helps in achieving the low power consumption and less area. Second stage is variable gain amplifier, uses current reuse technique as well as gm-boost technique and has constant dc current to make the input impedance stable. Source degeneration technique cancel out MOS parasitic capacitance help in achieving linearity. Simulated maximum peak gain is 13.139 dB at 30.57 GHz and lowest peak gain is 7.75 dB at 26 GHz i.e. approximately flat over the entire band. Lowest NF is 3.08 dB at 32.6 GHz. Process corner simulation has been done for all four corners (S–S, S–F, F–S, F–F) showing robustness of LNA. Input return loss has value less than − 9.58 dB while output return loss has less than − 2.6 dB showing good matching; power consumption is 16 mW for dc current of 16 mA at 1 V. MOS active chip area is 76.727 µm2.

Similar content being viewed by others

References

El-Nozahi, M., Sanchez-Sinencio, E., & Entesari, K. (2010). A millimeter-wave (23–32 GHz) wideband BiCMOS low-noise amplifier. IEEE Journal of Solid-State Circuits, 45(2), 289–299

Heidari, T., & Nabavi, A. (2020). Design and analysis of a wideband compact LNA-mixer in millimeter wave frequency. Analog Integrated Circuits and Signal Processing, 1–13.

Gebali, F., & Atef, I. (2014). Efficient scalable serial multiplier over GF (2m) based on trinomial. IEEE Transactions on Very Large Scale Integration (VLSI) Systems, 23(10), 2322–2326

Rivas-Torres, W., & Roth, Z. S. (2013). Determination and study of MOSFET technology current. Canadian Journal on Electrical and Electronics Engineering, 4(2), 75–82

Chang, Y.-T., & Hsin-Chia, Lu. (2019). A V-band low-power digital variable-gain low-noise amplifier using current-reused technique with stable matching and maintained OP1dB. IEEE Transactions on Microwave Theory and Techniques, 67(11), 4404–4417

Qin, P., & Xue, Q. (2017). Design of wideband LNA employing cascaded complimentary common gate and common source stages. IEEE Microwave and Wireless Components Letters, 27(6), 587–589

Shameli, A., & Heydari, P. (2006). A novel power optimization technique for ultra-low power RFICs. In Proceedings of the 2006 international symposium on Low power electronics and design (pp. 274–279). ACM.

Zhang, F., & Kinget, P. R. (2006). Low-power programmable gain CMOS distributed LNA. IEEE Journal of Solid-State Circuits, 41(6), 1333–1343

Heydari, P. (2007). Design and analysis of a performance-optimized CMOS UWB distributed LNA. IEEE Journal of Solid-State Circuits, 42(9), 1892–1905

Kumar, M., & Deolia, V. K. (2019). A wideband design analysis of LNA utilizing complimentary common gate stage with mutually coupled common source stage. Analog Integrated Circuits and Signal Processing, 98(3), 575–585

Lo, Y.-T., & Kiang, J.-F. (2011). Design of wideband LNAs using parallel-to series resonant matching network between common-gate and common source stages. IEEE Transactions on Microwave Theory and Techniques, 59(9), 2285–2294

Jussila, J., & Sivonen, P. (2008). A 1.2-V highly linear balanced noise-cancelling LNA in 0.13 µm CMOS. IEEE Journal of Solid-State Circuits, 43(3), 579–587

Fu, C.-T., Kuo, C.-N., & Taylor, S. (2010). Low-noise amplifier design with dual reactive feedback for broadband simultaneous noise and impedance matching. IEEE Transactions on Microwave Theory and Techniques, 58(4), 795–806

Borremans, J., Wambacq, P., Soens, C., Rolain, Y., & Kuijk, M. (2008). Low-area active-feedback low-noise amplifier design in scaled digital CMOS. IEEE Journal of Solid-State Circuits, 43(11), 2422–2433

Perumana, B. G., Zhan, J. H. C., Taylor, S. S., Carlton, B. R., & Laskar, J. (2008). Resistive-feedback CMOS low-noise amplifiers for multiband applications. IEEE Transactions on Microwave theory and Techniques, 56(5), 1218–1225

Chang, J., & Lin, Y. (2011). 0.99 mW 3–10 GHz common-gate CMOS UWB LNA using T-match input network and self-body-bias technique. Electronics Letters, 47(11), 658–659

Parvizi, M., Allidina, K., & El-Gamal, M. N. (2016). An ultra-low-power wideband inductorless CMOS LNA with tunable active shunt-feedback. IEEE Transactions on Microwave Theory and Techniques, 64(6), 1843–1853

Belmas, F., Hameau, F., & Fournier, J. M. (2012). A low power inductorless LNA with double gm enhancement in 130 nm CMOS. IEEE Journal of Solid-State Circuits, 47(5), 1094–1103

Bruccoleri, F., Klumperink, E. A., & Nauta, B. (2004). Wide-band CMOS low-noise amplifier exploiting thermal noise canceling. IEEE Journal of Solid-State Circuits, 39(2), 275–282

Ankathi, S., Vignan, S., Athukuri, S., et al. (2017). A 5–7 GHz current reuse and gm-boosted common gate low noise amplifier with LC based ESD protection in 32 nm CMOS. Analog Integrated Circuits and Signal Processing, 90, 573–589

Soleymani, F., Bastan, Y., Amiri, P., & Maghami, M. H. (2020). A 0.3–1.4 GHz inductorless CMOS variable gain LNA based on the inverter cell and self-forward-body-bias technique. AEU-International Journal of Electronics and Communications, 113, 152974

Park, H., Jung, S., & Chung, H. J. (2020). An analog correlator based CMOS analog front end with digital gain control circuit for hearing aid devices. Analog Integrated Circuits and Signal Processing, 105(2), 157–165

Zhang, F., & Kinget, P. (2006). Low-power programmable gain CMOS distributed LNA. IEEE Journal of Solid-State Circuits, 41(6), 1333–1343

Yu, Y.-H., Chen, Y.-J., & Heo, D. (2007). A 0.6-V low power UWB CMOS LNA. IEEE Microwave and Wireless Components Letters, 17(3), 229–231

Parvizi, M., Allidina, K., & El-Gamal, M. N. (2014). A sub-mW, ultra-low-voltage, wideband low-noise amplifier design technique. IEEE Transactions on Very Large Scale Integration (VLSI) Systems, 23(6), 1111–1122

Razavi, B. (2016). Design of analog CMOS integrated circuits. Tata McGraw Hill.

Liu, J. Y. C., Chen, J. S., Hsia, C., Yin, P. Y., & Lu, C. W. (2014). A wideband inductorless single-to-differential LNA in 0.18 µm CMOS technology for digital TV receivers. IEEE Microwave and Wireless Components Letters, 24(7), 472–474

Kim, J., & Silva-Martinez, J. (2012). Wideband inductorless balun-LNA employing feedback for low-power low-voltage applications. IEEE Transactions on Microwave Theory and Techniques, 60(9), 2833–2842

Wang, H., Zhang, Li., & Zhiping, Yu. (2010). A wideband inductorless LNA with local feedback and noise cancelling for low-power low-voltage applications. IEEE Transactions on Circuits and Systems I: Regular Papers, 57(8), 1993–2005

Liao, C.-F., & Liu, S.-I. (2007). A broadband noise-canceling CMOS LNA for 3.1–10.6-GHz UWB receivers. IEEE Journal of Solid-State Circuits, 42(2), 329–339

Chou, H. T., Chen, S. W., & Chiou, H. K. (2013). A low-power wideband dual-feedback LNA exploiting the gate-inductive bandwidth/gain-enhancement technique. In 2013 IEEE MTT-S international microwave symposium digest (MTT) (pp. 1–3). IEEE.

Kim, J., Hoyos, S., & Silva-Martinez, J. (2010). Wideband common-gate CMOS LNA employing dual negative feedback with simultaneous noise, gain, and bandwidth optimization. IEEE Transactions on Microwave Theory and Techniques, 58(9), 2340–2351

Guo, B., & Li, X. (2013). A 1.6–9.7 GHz CMOS LNA linearized by post distortion technique. IEEE Microwave and Wireless Components Letters, 23(11), 608–610

Author information

Authors and Affiliations

Corresponding author

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Kalra, D., Goyal, V. & Srivastava, M. Design and performance analysis of low power LNA with variable gain current reuse technique. Analog Integr Circ Sig Process 108, 351–361 (2021). https://doi.org/10.1007/s10470-021-01855-6

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10470-021-01855-6