Abstract

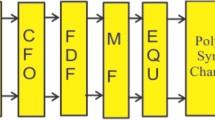

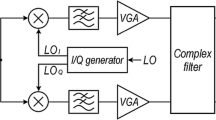

In this work, we present a new RF receiver architecture capable of addressing different RF bands and communication protocols. The frequency planning and discrete-time complex signal processing choices greatly simplify the frequency synthesis circuit. Since this is one of the most power-hungry blocks in the receiver, one can expect a reduction in power consumption. Thanks to the Bandpass Sampling (BPS) technique, the receiver addresses multiple RF bands without changing the sampling frequency. The BPS downconverts the signal to a varying Intermediate Frequencies (IF), called sliding IF. From this point on, the signal processing is in the discrete-time domain. The same clock is employed to drive a time-varying gain amplifier (TVGA), which implements a mixing process by multiplying the input with a sine or cosine centered at IF. A Double-Quadrature Low-IF frequency planning and complex signal processing avoid the problem of image signal folding in both downconversions. Behavioral modeling shows how this architecture can be utilized for LTE and IEEE802.11g standards, fulfilling the noise, linearity, and image rejection specifications. With 6 bits resolution in the TVGA gains, the quantized sine and cosine lead to a Signal-to-Distortion Ratio of 48dB. The receiver achieves an image rejection of 55dB for the LTE standard and 42dB for IEEE802.11g.

Similar content being viewed by others

References

Staszewski, R. B., Muhammad, K., Leipold, D., Hung, C.-M., Ho, Y.-C., Wallberg, J. L., et al. (2004). All-digital tx frequency synthesizer and discrete-time receiver for bluetooth radio in 130-nm CMOS. IEEE Journal of Solid-State Circuits, 39(12), 2278–2291.

Mitola, J. (1995). The software radio architecture. IEEE Communications Magazine, 33(5), 26–36.

Kale, A., Popuri, S., Koeberle, M., Sturm, J., & Pasupureddi, V. S. R. (2019). A -40 dB EVM, 77 MHz dual-band tunable gain sub-sampling receiver front end in 65-nm CMOS. IEEE Transactions on Circuits and Systems I: Regular Papers, 66(3), 1166–1179.

Bazrafshan, A., Taherzadeh-Sani, M., & Nabki, F. (2018). A 0.8-4-GHz software-defined radio receiver with improved harmonic rejection through non-overlapped clocking. IEEE Transactions on Circuits and Systems I: Regular Papers, 65(10), 3186–3195.

Muhammad, K., Ho, Y. C., Mayhugh, T., Hung, C. M., Jung, T., Elahi, I., et al. (2005). A discrete time quad-band GSM/GPRS receiver in a 90nm digital CMOS process, In Proceedings of the IEEE 2005 Custom Integrated Circuits Conference, 2005 (pp. 809–812).

Bagheri, R., Mirzaei, A., Chehrazi, S., Heidari, M. E., Lee, M., Mikhemar, M., et al. (2006). An 800-mhz-6-ghz software-defined wireless receiver in 90-nm cmos. IEEE Journal of Solid-State Circuits, 41(12), 2860–2876.

Geis, A., Ryckaert, J., Bos, L., Vandersteen, G., Rolain, Y., & Craninckx, J. (2010). A 0.5 mm\(^2\) power-scalable 05–38-GHz CMOS DT-SDR receiver with second-order RF band-pass sampler. IEEE Journal of Solid-State Circuits, 45(11), 2375–2387.

Chen, R., & Hashemi, H. (2014). A 0.5-to-3 GHz software-defined radio receiver using discrete-time RF signal processing. IEEE Journal of Solid-State Circuits, 49(5), 1097–1111.

Madadi, I., Tohidian, M., Cornelissens, K., Vandenameele, P., & Staszewski, R. B. (2016). A High IIP2 SAW-less superheterodyne receiver with multistage harmonic rejection. IEEE Journal of Solid-State Circuits, 51(2), 332–347.

Tohidian, M., Madadi, I., & Staszewski, R. B. (2017). A fully integrated discrete-time superheterodyne receiver. IEEE Transactions on Very Large Scale Integration (VLSI) Systems, 25(2), 635–647.

Jakonis, D., Folkesson, K., Dbrowski, J., Eriksson, P., & Svensson, C. (2005). A 2.4-ghz RF sampling receiver front-end in 0.18-um cmos. IEEE Journal of Solid State Circuits, 40(6), 1265–1277.

Heragu, A., Ruffieux, D., & Enz, C. C. (2013). A 2.4-GHz MEMS-based PLL-free multi-channel receiver with channel filtering at RF. IEEE Journal of Solid-State Circuits, 48(7), 1689–1700.

Cheng, J., Qi, N., Chiang, P. Y., Natarajan, A., & Low-Power, A. (2014). Low-voltage WBAN-compatible sub-sampling PSK receiver in 65 nm CMOS. IEEE Journal of Solid-State Circuits, 49(12), 3018–3030.

Behjou, N., Larsen, T., Hoegdal, M. (2008). Design of a simultaneous multi-band RF sub-sampling receiver, 2008 IEEE MTT-S International Microwave Symposium Digest, pp. 5-8.

Klumperink, E. A. M., Soer, M. C. M., Struiksma, R. E., van Vliet, F. E., & Nauta, B. (2016). Towards Low Power N-Path Filters for Flexible RF-Channel Selection. US: Springer International Publishing.

Klumperink, E. A. M., Westerveld, H. J.,Nauta, B. (2017). N-path filters and Mixer-First Receivers: A Review, 2017 IEEE Custom Integrated Circuits Conference (CICC), pp. 1-8.

Xu, Y., Zhu, J., & Kinget, P. R. (2018). A blocker-tolerant RF front end with harmonic-rejecting N-path filter. IEEE Journal of Solid-State Circuits, 53(2), 327–339.

Akbar, H., & Abumoslem, J. (2021). A higher-order highly linear N-path band-pass filter. Circuits, Systems, and Signal Processing, 40(1), 50–69.

Mohammad, E., Mahdi, T., & Ali, J. (2018). A wideband receiver front-end using 1st and 3rd harmonics of the N-path filter response. Analog Integrated Circuits and Signal Processing, 94(3), 451–467.

Li, Y., Bakkaloglu, B., & Chakrabarti, C. (2007). A system level energy model and energy-quality evaluation for integrated tranceivers front-ends. IEEE Transactions on Very Large Scale Integration (VLSI) Systems, 15(1), 90–103.

Valkama, M., Renfors, M., & Koivunen, V. (2001). Advanced methods for I/Q imbalance compensation in communication receivers. IEEE Transactions on Signal Processing, 49(10), 2335–2344.

Kroupa, V. F. (1998). Direct Digital Frequency Synthesizers. John Wiley & Sons.

Gilbert, B. (1968). A precision four-quadrant multiplier with subnanosecond response. IEEE Journal of Solid-State Circuits, 3(4), 365–373.

Proakis, J. G., & Salehi, M. (2008). Digital Communications. New York: McGraw-Hill.

Vaughan, R. G., Scott, N. L., & White, D. R. (1991). The theory of bandpass sampling. IEEE Transactions on Signal Processing, 39(9), 1973–1984.

Sun,Y.-R. (2006). Generalized bandpass sampling receivers for software defined radio, Doctoral Dissertation, Royal Institute of Technology.

ETSI 3rd Generation Partnership Project, LTE; Evolved Universal Terrestrial Radio Access (E-UTRA); User Equipment (UE) radio transmission and reception (3GPP TS 36.101 version 12.5.0 Release 12) (2014).

Eriksson, P., Tenhunen,H. The noise figure of a sampling mixer: theory and mesurement, ICECS’99 Proceedings of ICECS ’99 6th IEEE International Conference on Electronics, Circuits ans Systems (Cat. No.99EX357), vol. 2, pp.899-902

Rhee, W., Xu, N., Zhou, B., & Wang, Z. (2013). Fractional-N frequency synthesis: overview and practical aspects with FIR-embedded design. Journal of Semiconductor Technology and Science, 13(2), 170–183.

IEEE Standard for Information technology-Telecommunications and information exchange between systems Local and metropolitan area networks-Specific requirements Part 11: Wireless LAN Medium Access Control (MAC) and physical layer (PHY) Specifications, IEEE Std 802.11-2012 (Revision of IEEE Std 802.11-2007), pp. 1-2793 (2012).

Gu, Q. (2006). RF System Design of Transceivers for Wireless Communications. US: Springer.

Lolis, L., Pelissier, M., Bernier, C., Dallet, D., Begueret, J. (2009). System design of bandpass sampling RF receivers, 2009 16th IEEE International Conference on Electronics, Circuits ans Systems - (ICECS 2009), pp. 691-694

de Souza, M., Mariano, A., & Taris, T. (2017). Reconfigurable inductorless wideband CMOS LNA for wireless communications. IEEE Transactions on Circuits and Systems I: Regular Papers, 64(3), 675–685.

Mohamed, M. A., & Abd-ElAtty, H. M. (2014). Performance analysis of LTE-advanced physical layer. International Journal of Computer Science Issues. https://doi.org/10.1109/ICCCIS48478.2019.8974494.

Otefa, A. M., ElBoghdadly, N. M., Sourour,E. A. (2007). Performance analysis of 802.11n wireless LAN physical layer, 2007 ITI 5th International Conference on Information and Communications Technology, pp. 279-288

Iniewski, K. (2007). Wireless Technologies: Circuits. Systems and Devices: CRC Press.

Shafik, R. A., Rahman, M. S., Islam,A. R. (2006) On the Extended Relationships Among EVM, BER and SNR as Performance Metrics, 2006 International Conference on Electrical and Computer Engineering, pp. 408-411

Author information

Authors and Affiliations

Corresponding author

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Lolis, L.H.A., Sionek, G., Mariano, A.A. et al. A discrete-time double-quadrature low-IF receiver for multi-standard and multi-carrier applications. Analog Integr Circ Sig Process 108, 335–349 (2021). https://doi.org/10.1007/s10470-021-01832-z

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10470-021-01832-z