Abstract

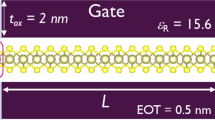

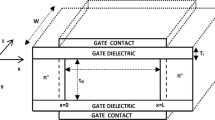

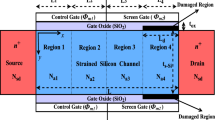

Enhancing the performance of Si field-effect transistors with ultrashort gate length is very challenging because of the increase of the source-to-drain tunneling and other short-channel effects. Doping engineering can affect the tunneling probability by varying the energy band profile and electric field. Full quantum ballistic simulations are performed here to study the use of doping engineering as a tool to improve the electrostatic integrity in a pMOSFETs device with a double-gate structure and a gate length of 5 nm. The simulation methodology is based on nonequilibrium Green’s functions, employing a six-band k·p Hamiltonian. The influence of the source/drain doping profile/concentration on the electric field in both the transport and confinement directions is also discussed. The trends found for the ON- to OFF-state current ratio and the switching delay differ, depending on the doping profile/concentration for high-performance and low-operating-power applications. The results of this study highlight the importance of using a Gaussian doping profile, as compared with constant doping, to improve the performance of such ultrascaled devices in terms of enhancing the subthreshold swing, reducing the drain-induced barrier lowering, and achieving low source-to-drain tunneling. The doping concentration can be optimized by controlling the source-to-drain tunneling and overcoming the source exhaustion. The selection of a certain damping factor in the Gaussian function can be used as a parameter, in addition to the peak doping concentration, to optimize the device performance.

Similar content being viewed by others

References

Radamson, H.H., He, X., Zhang, Q., Liu, J., Cui, H., Xiang, J., Kong, Z., Xiong, W., Li, J., Gao, J., Yang, H., Gu, S., Zhao, X., Du, Y., Yu, J., Wang, G.: Miniaturization of CMOS. Micromachines 10(5), 293 (2019)

Bhattacharya, D., Jha, N.K.: FinFETs: From devices to architectures. Hindawi Publ. Corp. Adv. Electron. 2014, 21–55 (2014). https://doi.org/10.1017/CBO9781316156148.003

Lundstrom, M., Ren, Z.: Essential physics of carrier transport in nanoscale MOSFETs. IEEE Trans. Electron Devices. 49, 133–141 (2002). https://doi.org/10.1109/16.974760

Tsividis, Y., McAndrew, C.: Operation and modeling of the MOS transistor. Oxford University Press, Oxford (2011)

Walls, T.J., Sverdlov, V.A., Likharev, K.K.: MOSFETs below 10nm: quantum theory. Phys. E: Low-Dimens. Sys. Nanostruct. 19(1–2), 23–27 (2003). https://doi.org/10.1016/S1386-9477(03)00288-1

Long, P., Huang, J.Z., Povolotskyi, M., Klimeck, G., Rodwell, M.J.W.: High-current tunneling FETs with (110) orientation and a channel heterojunction. IEEE Electron Device Lett. 37(3), 345–348 (2016)

Anantram, M.P., Lundstrom, M.S., Nikonov, D.E.: Modeling of nanoscale devices. Proc. IEEE. 96, 1509–1510 (2008). https://doi.org/10.1109/JPROC.2008.927311

Kim, R., Avci, U.E., Young, I.A.: Source/drain doping effects and performance analysis of ballistic III-V n-MOSFETs. IEEE J. Electron Devices Soc. 3, 37–43 (2015). https://doi.org/10.1109/JEDS.2014.2363389

Lin, H., Taur, Y.: Effect of source-drain doping on subthreshold characteristics of short-channel DG MOSFETs. IEEE Trans. Electron Devices 64(12), 4856–4860 (2017)

Rahimian, M., Orouji, A.A.: Nanoscale SiGe-on-insulator (SGOI) MOSFET with graded doping channel for improving leakage current and hot-carrier degradation. Superlattices Microstruct. 50, 667–679 (2011). https://doi.org/10.1016/j.spmi.2011.09.008

Veloso, A., Matagne, P., Simoen, E., Kaczer, B., Eneman, G., Mertens, H.: Junctionless versus inversion-mode lateral semiconductor nanowire transistors. J. Phys. Condens. Matter. (2018). https://doi.org/10.1088/1361-648X/aad7c7

Zhang, S., Huang, J.Z., Khaliq, A., Xie, H., Chen, W., Yin, W.Y.: Quantum transport study of Si ultrathin-body double-gate pMOSFETs: I-V, C-V, energy delay, and parasitic effects. IEEE Trans. Electron Devices. 66, 655–663 (2019). https://doi.org/10.1109/TED.2018.2881160

Yadav, D., Nair, D.R.: Impact of source to drain tunneling on the ballistic performance of Si, Ge, GaSb, and GeSn nanowire p-MOSFETs. IEEE J. Electron Devices Soc. 8, 308–315 (2020). https://doi.org/10.1109/JEDS.2020.2980633

Teherani, J.T.: A comprehensive theoretical analysis of hole ballistic velocity in Si, SiGe, and Ge: effect of uniaxial strain, crystallographic orientation, body thickness, and gate architecture. IEEE Trans. Electron Devices. 64, 3316–3323 (2017). https://doi.org/10.1109/TED.2017.2708691

Jeong, K., and Kahng, A.B. Semiconductor Industry Association.(2017). International Technology Roadmap on Semiconductors., (2009) www.itrs.net

Madelung, O., von der Osten, W., Rössler, U.: Semiconductors: Intrinsic Properties of Group IV Elements and III-V, IIVI, and I-VII Compounds. Springer, Berlin (1987)

Moussavou, M., Cavassilas, N., Dib, E., Bescond, M.: Influence of uniaxial strain in Si and Ge p-type double-gate metal-oxide-semiconductor field effect transistors. J. Appl. Phys. DOI 10(1063/1), 4930567 (2015)

Singh, B., Gola, D., Singh, K., Goel, E., Kumar, S., Jit, S.: Analytical modeling of channel potential and threshold voltage of double-gate junctionless FETs with a vertical Gaussian-like doping profile. IEEE Trans. Electron Devices. 63, 2299–2305 (2016). https://doi.org/10.1109/TED.2016.2556227

Huang, J.Z., Chew, W.C., Peng, J., Yam, C.Y., Jiang, L.J., Chen, G.H.: Model order reduction for multiband quantum transport simulations and its application to p-type junctionless transistors. IEEE Trans. Electron Devices. 60, 2111–2119 (2013). https://doi.org/10.1109/TED.2013.2260546

Taur, Y., Ning, T.H.: Fundamentals of modern VLSI devices. Cambridge University Press, Cambridge (1988)

Datta, S.: Quantum transport: atom to transistor. Cambridge University Press, Cambridge (2005)

Datta, K., Khosru, Q.D.M.: III-V Tri-gate quantum well MOSFET: quantum ballistic simulation study for 10nm technology and beyond. Solid-State Electron. 118, 66–77 (2016)

Sze, S.M., Ng, K.K.: Physics Of Semiconductor devices. Wiley, New Jersy (2007)

Rahman, A., Guo, J., Datta, S., Lundstrom, M.S.: Theory of ballistic nanotransistors. IEEE Trans. Electron Devices. 50, 1853–1864 (2003). https://doi.org/10.1109/TED.2003.815366

Ferhati, H., Djeffal, F.: Graded channel doping junctionless MOSFET:a potential high performance and low power leakage device for nanoelectronic applications. J. Comput. Electron 17(1), 129–137 (2018)

Andrei, P., Mayergoyz, I.: Random doping-induced fluctuations of subthreshold characteristics in MOSFET devices. Solid. State. Electron. 47, 2055–2061 (2003). https://doi.org/10.1016/S0038-1101(03)00236-3

Liu, K.M., Chen, E.C.: Investigation of the effects and the random-dopant-induced variations of source/drain extension of 7-nm strained SiGe n-type FinFETs. IEEE Trans. Electron Devices. 66, 847–854 (2019). https://doi.org/10.1109/TED.2018.2884246

Author information

Authors and Affiliations

Corresponding author

Additional information

Publisher’s Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Khaliq, A., Zhang, S. Doping engineering to enhance the performance of double-gate pMOSFETs with ultrashort gate length (5 nm). J Comput Electron 20, 1178–1186 (2021). https://doi.org/10.1007/s10825-021-01693-9

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10825-021-01693-9