Abstract

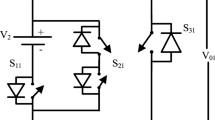

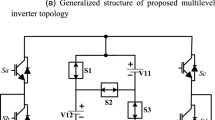

In this paper, firstly, a new basic structure is proposed, and then, the extended structure which is made up of the series connection of the basic units is proposed. Two algorithms are presented to calculate the magnitude of DC voltage sources in order to generate all positive and negative voltage levels (even and odd) at the output. The suggested structure is optimized to generate the maximum number of output voltage levels using the minimum number of components, gate driver circuits, DC voltage sources, minimum variety of DC voltage sources and less blocking voltage on the switches. Fewer numbers of components and variety of DC voltage sources are the main advantages of the proposed topology which lead to lower cost and control complexity. The mentioned advantages are verified by comparison studies of the proposed cascaded topology with most of the other recently presented topologies. Finally, the performance of the proposed topology is confirmed by the experimental results.

Similar content being viewed by others

References

Ali JSM, Alishah RS, Krishnasamy V (2018) A new symmetric multilevel converter topology with reduced voltage on switches and DC source. In: 2018 international conference on power, instrumentation, control and computing (PICC), 2018. IEEE, pp 1–6

Alishah RS, Hosseini SH, Babaei E, Sabahi M (2016a) A new general multilevel converter topology based on cascaded connection of submultilevel units with reduced switching components DC sources, and blocked voltage by switches. IEEE Trans Ind Electron 63:7157–7164

Alishah RS, Hosseini SH, Babaei E, Sabahi M (2016b) Optimal design of new cascaded switch-ladder multilevel inverter structure. IEEE Trans Ind Electron 64:2072–2080

Alishah RS, Babaei E, Hosseini SH, Sabahi M (2018a) A developed two-leg ladder multilevel converter structure. J Circuits Syst Comput 27:1850183

Alishah RS, Hosseini SH, Babaei E, Sabahi M, Ardashir JF (2018b) An improved symmetric H-bridge multilevel converter topology; an attempt to reduce power losses. J Circuits Syst Comput 27:1850187

Babaei E (2010) Optimal topologies for cascaded sub-multilevel converters. J Power Electron 10:251–261

Babaei E, Hosseini SH (2009) New cascaded multilevel inverter topology with minimum number of switches. Energy Convers Manag 50:2761–2767

Banaei MR, Khounjahan H, Salary E, Dehghanzadeh A (2012) Multi transformer cell inverter with reduced dc sources. Gazi Univ J Sci 25:697–705

Babaei E, Alilu S, Laali S (2013a) A new general topology for cascaded multilevel inverters with reduced number of components based on developed H-bridge. IEEE Trans Ind Electron 61:3932–3939

Babaei E, Kangarlu MF, Hosseinzadeh MA (2013b) Asymmetrical multilevel converter topology with reduced number of components IET Power. IET Power Electron 6:1188–1196

Babaei E, Laali S (2015) Optimum structures of proposed new cascaded multilevel inverter with reduced number of components. IEEE Trans Ind Electron 62:6887–6895

Barzegarkhoo R, Kojabadi HM, Zamiry E, Vosoughi N, Chang L (2015) Generalized structure for a single phase switched-capacitor multilevel inverter using a new multiple DC link producer with reduced number of switches. IEEE Trans Power Electron 31:5604–5617

Chen W, Hotchkiss E, Bazzi A (2018) Reconfiguration of NPC multilevel inverters to mitigate short circuit faults using back-to-back switches CPSS. Trans Power Electron Appl 3:46–55

Ebrahimi J, Babaei E, Gharehpetian GB (2011) A new topology of cascaded multilevel converters with reduced number of components for high-voltage applications. IEEE Trans Power Electron 26:3109–3118

Eltawil MA, Zhao Z (2010) Grid-connected photovoltaic power systems: Technical and potential problems—a review. Renew Sustain Energy Rev 14:112–129

Gautam SP, Sahu LK, Gupta S (2016) Reduction in number of devices for symmetrical and asymmetrical multilevel inverters. IET Power Electron 9:698–709

Hinago Y, Koizumi H (2009) A single-phase multilevel inverter using switched series/parallel dc voltage sources. IEEE Trans Ind Electron 57:2643–2650

Jahan HK, Tarzamni H, Kolahian P, Hosseini SH, Tahami F, Blaabjerg F (2019) A switched-capacitor inverter with optimized switch-count considering load power factor. In: IECON 2019—45th annual conference of the ieee industrial electronics society, 2019. IEEE, pp 4959–4964

Kadir MA, Mekhilef S, Ping H (2010) Voltage vector control of a hybrid three-stage 18-level inverter by vector decomposition. IET Power Electron 3:601–611

Kangarlu MF, Babaei E (2012) A generalized cascaded multilevel inverter using series connection of submultilevel inverters. IEEE Trans Power Electron 28:625–636

Kangarlu MF, Babaei E (2013) Cross-switched multilevel inverter: an innovative topology. IET Power Electron 6:642–651

Khenar M, Taghvaie A, Adabi J, Rezanejad M (2018) Multi-level inverter with combined T-type and cross-connected modules. IET Power Electron 11:1407–1415

Khosroshahi MT (2014) Crisscross cascade multilevel inverter with reduction in number of components. IET Power Electron 7:2914–2924

Lee SS, Sidorov M, Lim CS, Idris NRN, Heng YE (2017) Hybrid cascaded multilevel inverter (HCMLI) with improved symmetrical 4-level submodule. IEEE Trans Power Electron 33:932–935

Naderi-Zarnaghi Y, Karimi M, Jannati-Oskuee M, Hosseini S, Najafi-Ravadanegh S (2018) A Developed Asymmetric Multilevel Inverter with Lower Number of Components. AUT J Electr Eng 50:197–206

Naderi Y, Hosseini SH, Zadeh SG, Mohammadi-Ivatloo B, Savaghebi M, Guerrero JM (2019) An optimized direct control method applied to multilevel inverter for microgrid power quality enhancement. Int J Electr Power Energy Syst 107:496–506

Nair V, Gopakumar K, Franquelo LG (2017) A very high resolution stacked multilevel inverter topology for adjustable speed drives. IEEE Trans Ind Electron 65:2049–2056

Oskuee MRJ, Karimi M, Naderi Y, Ravadanegh SN, Hosseini SH (2017) A new multilevel voltage source inverter configuration with minimum number of circuit elements. J Central South Univ 24:912–920

Saeidabadi S, Gandomi AA, Hosseini SH, Sabahi M, Gandomi YA (2017) New improved three-phase hybrid multilevel inverter with reduced number of components. IET Power Electron 10:1403–1412

Singhai S, Pandey A, Singh V (2018) New topology of asymmetrical multilevel inverter [15/29 Level]. In: 2018 International conference on current trends towards converging technologies (ICCTCT), 2018. IEEE, pp 1–6

Zamiri E, Vosoughi N, Hosseini SH, Barzegarkhoo R, Sabahi M (2016) A new cascaded switched-capacitor multilevel inverter based on improved series–parallel conversion with less number of components. IEEE Trans Ind Electron 63:3582–3594

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Naderi, R., Babaei, E., Sabahi, M. et al. Optimization and Implementation of a New Topology for Cascaded Multilevel Inverters with Reduced Number of Semiconductor Devices. Iran J Sci Technol Trans Electr Eng 45, 959–977 (2021). https://doi.org/10.1007/s40998-020-00401-w

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s40998-020-00401-w