Abstract

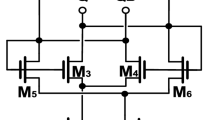

In this paper, a CMOS mm-wave phase locked loop (PLL) with improved voltage controlled oscillator (VCO) and injection-locked frequency divider (ILFD) at operational harmonic frequency 125 GHz is presented. The VCO structure uses the bulk effective and MOS varactor capacitor to adjust parasitic capacitor of the cross coupled pair. It obtains 2th harmonic frequency with 24% tuning range (110–140 GHz) by applying ± 1.2 V input voltage variation. The divide-by-4 ILFD circuit uses a cross coupled VCO with three injection transistors acting in linear and nonlinear regions. The frequency dividers such as divided-by-4 ILFD, subsequent current mode logic (CML) and true single phase clock (TSPC) as divider chain with ratio 1/256 are used to synthesize frequency 244 MHz which is compared to reference frequency, 244 MHz in the PLL. Simulation results of the proposed PLL circuit are obtained after extracting post layout (with total chip size of 0.29 mm2) in 65 nm CMOS standard technology and @ 1.2 V power supply voltage. The obtained results confirm theoretical relations and indicate that the proposed circuit has good figure of merit (FoM), and higher tuning range and lower die area than the recent designs.

Similar content being viewed by others

References

Öjefors, E., Heinemann, B., Pfeiffer, U. R. (2011). Active 220- and 325-GHz frequency multiplier chains in an SiGe HBT technology. In IEEE transactions on microwave theory and techniques, Vol. 59, No. 5

Wu, C.Y., Chen, M. C., Lo, Y. K. (2009) a phase-locked loop with injection-locked frequency multiplier in 0.18um CMOS for V-Band Applications. In IEEE transactions on microwave theory and techniques, Vol. 57, No. 7

Jain, S., Zhang, N., Belostotski, L. (2018). A 167-to-172 GHz 65-nm CMOS body-voltage-tuned harmonic-mode voltage controlled oscillator. Microwave and Optical Technology Letters, pp. 1–4.

Jain, S., Zhang, N., Belostotski, L. (2017). Millimeter-wave CMOS PLL Using a Push-Push Oscillator. In 2017 IEEE 30th Canadian conference on electrical and computer engineering (CCECE)

Razavi, B. (2012). RF Microelectronics", Prentice Hall Communications Engineering and Emerging Technologies Series from Ted Rappaport, 2nd edition

Jang, S. L., & Huang, Y. C. (2017). Wide-locking range ÷3 injection-locked frequency divider using direct-injection and switching-injection techniques. IET Microwaves, Antennas and Propagation, 11(12), 1803–1809.

Jang, S. L., Huang, J. F., & Lin, F. B. (2015). Wide-locking range LC-tank divide-by-4 injection-locked frequency divider using transformer feedback. International Journal of RF and Microwave Computer-Aided Engineering/Vol., 25(7), 557–562.

Chang, C. W., & Jang, S. L. (2014). LC-tank divide-by-4 injection-locked frequency divider using the second-order harmonic feedback. International Journal of Electronics, 101(2), 204–211.

Jang, S. L., Kung, T. C., Hsue, C. W. (2017). Wide-locking range divide-by-4 injection-locked frequency divider using linear mixer approach. In IEEE microwave and wireless components letters, vol. 27, No. 4

Zhang, L., Lin, L., Zhu, X., Wang, Y. (2017). A 140GHz Phase-Locked Loop with 14.3% locking range in 65-nm CMOS. In 2017 International conference on electron devices and solid-state circuits (EDSSC)

S. Jain, N. Zhang, " A 171 GHz harmonic-mode PLL with − 14.2 dBm output power in 65 nm CMOS. Analog Integr Circ Sig Process 98, 643–649 (2019).

Cao, C. (2005). A Power Efficient 26-GHz 32:1 Static Frequency Divider in 130-nm Bulk CMOS. In IEEE microwave and wireless components letters, Vol. 15, Issue 11

Razavi, B. (2016). TSPC Logic (A circuit for all seasons). In IEEE Solid-State Circuits Magazine, Vol. 8, Issue 4

Nam, W., Son, J., Shin, H. (2015). Design of a 40GHz PLL Frequency Synthesizer with Wide Locking Range ILFD in 65nm CMOS. In 2015 International SoC Design Conference (ISOCC)

Kim, N., Song, K., Yun, J., Yoo, J. Rieh, J. S. (2016). Two 122-GHz Phase-Locked Loops in 65-nm CMOS Technolog. In IEEE transactions on microwave theory and techniques, Vol. 64, Issue 8

Lin, B.Y., Liu, S. I. (2011). A 132.6-GHz Phase-Locked Loop in 65 nm Digital CMOS. In IEEE transactions on circuits and systems II: Express Briefs, Vol. 58, Issue 10

Tan, K. W., Chu, T. S., Hsu, S. S. H. (2015). A 76.2–89.1 GHz Phase-Locked Loop With 15.6% Tuning Range in 90 nm CMOS for W-Band Applications. In IEEE microwave and wireless components letters, Vol. 25, Issue 8

Acknowledgements

The authors would like to thank all people involved in this research work for their kind and responsible assistance special to Dr. Mahdi Mottaghi-Kashtiban.

Author information

Authors and Affiliations

Corresponding author

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Neda, S., Yosefi, G. & Eskandarian, A. A 125 GHz millimeter-wave phase lock loop with improved VCO and injection-locked frequency divider in 65 nm CMOS process. Analog Integr Circ Sig Process 107, 483–496 (2021). https://doi.org/10.1007/s10470-021-01822-1

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10470-021-01822-1