Abstract

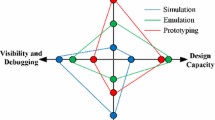

Because of the shrinking transistor size and improved design process, the computation capability of modern digital systems has increased tremendously over the past few years. This, however, has led to increased design complexity and huge verification efforts and costs. The design of new digital systems costs millions of dollars and the money is wasted if the final product does not serve the purpose. This has made pre-silicon verification even more pertinent as it can detect design faults prior to its roll out and can save companies a huge fortune. Pre-silicon verification now accounts for almost 70% of the total design effort and cost of modern digital systems. For pre-silicon verification, four techniques are commonly used namely simulation, emulation, virtual prototyping and FPGA-based prototyping. These techniques have their advantages and disadvantages. However, FPGA-based prototyping is unique in the sense it gives better speed and real world testing experience as compared to other pre-silicon verification techniques. In this paper, we give a detailed survey of multi-FPGA prototyping. A survey of three different multi-FPGA platforms namely off-the-shelf, custom, and cabling platform is presented in this work. A comprehensive overview of these platforms from hardware perspective is presented. Detailed discussion on their respective back end flow and the associated difference is also presented. The survey is concluded with a discussion on the challenges faced by multi-FPGA prototyping and the research opportunities where work can be done for further improvement.

Similar content being viewed by others

References

Aldec: The design verification company (2020) https://www.aldec.com/en

Alpert CJ, Chan T, Huang D, Kahng A, Markov I, Mulet P, and Yan K (1997) “Faster Minimization of Linear Wirelength for Global Placement,” ACM Symposium on Physical Design, pp. 4–11

Alpert CJ, Hagen LW, and Kahng AB (1997) “Multilevel Circuit Partitioning,” Design Automation Conference, pp. 530–533

Altera (2020) http://www.altera.com

AMD (2007) http://techreport.com/news/13721/chip-problem-limits-supply-of-quad-core-opterons

Auspy (2020) https://www.mentor.com/products/fv/aupsy

Avnet: Simulation and verification services (2020) http://www.avid-tech.com/services/pcb-design-and-simulation/simulation-and-verification-services/

Babb J, Tessier R, Dahl M, Hanono S, Hoki D, Agarwal A (1997) Logic emulation with virtual wires. Computer-Aided Design of Integrated Circuits and Systems, IEEE Transactions on 16(6):609–626

Berkeley, ABC: A System for Sequential Synthesis and Verification (2007) http://www.eecs.berkeley.edu/alanmi/abc/

Bui TN, Moon BR (1994) “A fast and stable hybrid genetic algorithm for the ratio-cut partitioning problem on hypergraphs,” in 31st Design Automation Conference. IEEE 664–669

Cadence protium platform (2020) https://www.cadence.com/en_US/home/tools/system-design-and-verification/fpga-basedprototyping/protium-s1-fpga-based-prototyping-platform.html

Cadence virtual system platform (2020) https://www.cadence.com/en_US/home/tools/system-design-and-verification/software-driven-verification/virtual-system-platform.html

Certify partitioning tool by synopsys (2017) http://www.synopsys.com/Prototyping/FPGABasedPrototyping/Pages/Certify.aspx

Chan PK, Schlag MD, Zien JY (1994) Spectral k-way ratio-cut partitioning and clustering. IEEE Transactions on computer-aided design of integrated circuits and systems 13(9):1088–1096

DiniGroup (2020) http://www.dinigroup.com/

Dunlop A, and Kernighan B (1985) “A Procedure for Placement of Standard-cell VLSI Circuits,” IEEE Transactions on CAD, pp. 92–98

Farooq U, Baig I, and Alzahrani BA (2018) “An efficient inter-fpga routing exploration environment for multi-fpga systems,” IEEE Access, vol. 6, pp. 56. 301–56-310

Farooq U, Chotin-Avot R, Azeem M, Ravoson M, and Mehrez H (2018) “Novel architectural space exploration environment for multi-fpga based prototyping systems,” Microprocessors and Microsystems, vol. 56, pp. 169 – 183. [Online]. Available: http://www.sciencedirect.com/science/article/pii/S0141933117300091

Farooq U, Mehrez H, Bhatti MK (2018) Inter-fpga interconnect topologies exploration for multi-fpga systems. Design Automation for Embedded Systems 22(1–2):117–140

Farooq U, Parvez H, Mehrez H, and Marrakchi Z (2011) Exploration of heterogeneous fpga architectures, Int. J. Reconfig. Comput., vol. 2011, pp. 2:1–2:18, Jan. 2011. [Online]. Available: http://dx.doi.org/10.1155/2011/121404

Farooq U, Parvez H, Mehrez H, Marrakchi Z (2012) A new heterogeneous tree-based application specific fpga and its comparison with mesh-based application specific fpga. Microprocessors and Microsystems 36(8):588–605

Fiduccia CM, and Mattheyeses RM (1982) “A Linear-time Heuristic for Improving Network Partitions,” Design Automation Conference, pp. 175–181

Flexras (2020) https://www.mentor.com/products/fv/flexras

Garey MR, Johnson DS (1990) Computers and Intractability; A Guide to the Theory of NP-Completeness. W. H. Freeman & Co., New York, NY, USA

Grimm T, Lettnin D, Hübner M (2018) A survey on formal verification techniques for safety-critical systems-on-chip. Electronics 7(6):81

Guo X, Dutta RG, Jin Y, Farahmandi F, and Mishra P (2015) Pre-silicon security verification and validation: A formal perspective, in Proceedings of the 52nd Annual Design Automation Conference, pp. 1–6

Hagen L, Kahng AB (1992) New spectral methods for ratio cut partitioning and clustering. IEEE transactions on computer-aided design of integrated circuits and systems 11(9):1074–1085

Haps multi-fpga board by synopsys (2020) http://www.synopsys.com/Prototyping/FPGABasedPrototyping/Pages/HAPS.aspx

Haps protocompiler by synopsys (2020) http://www.synopsys.com/Prototyping/FPGABasedPrototyping/Pages/protocompiler.aspx

Hauck S, and Borriello G (1995) “Logic partition orderings for multi-fpga systems,” in Proceedings of the 1995 ACM third international symposium on Field-programmable gate arrays, pp. 32–38

Hauck S, DeHon A (2007) Reconfigurable Computing: The Theory and Practice of FPGA-Based Computation. Morgan Kaufmann Publishers Inc., San Francisco, CA, USA

Hennessy P, (2011) Computer Architecture: A Quantitative Approach, 5th; ed. Morgan Kauffman

Huang CY, Yin YF, Hsu CJ, Huang TB, Chang TM (2011) “Soc hw/sw verification and validation,” in 16th Asia and South Pacific Design Automation Conference (ASP-DAC). IEEE 2011:297–300

Huang D, and Kahng A (1997) “Partitioning-based Standard-cell Global Placement with an Exact Objective,” ACM Symposium on Physical Design, pp. 18–25

Ic insights (2018) https://www.icinsights.com/news/bulletins/Automotive-And-IoT-Will-Drive-IC-Growth-Through-2021/

Inagi M, Takashima Y, and Nakamura Y (2009) “Globally optimal time-multiplexing in inter-fpga connections for accelerating multi-fpga systems,” in Field Programmable Logic and Applications, 2009. FPL 2009. International Conference on, pp. 212–217

Intel, Quartus prime, https://www.intel.com/content/www/us/en/software/programmable/quartus-prime/overview.html

Karypis G, Aggarwal R, Kumar V, and Shekhar S (1997) “Multilevel Hypergraph Partitioning: Application in VLSI Design,” Design Automation Conference, pp. 526–529

Karypis G, and Kumar V (1999) “Multilevel k-way Hypergraph Partitioning,” Design automation conference

Kern C, Greenstreet MR (1999) Formal verification in hardware design: a survey. ACM Transactions on Design Automation of Electronic Systems (TODAES) 4(2):123–193

Kernighan B, Lin S (1970) An Efficient Heuristic Procedure for Partitioning Graphs. Bell System Tech. Journal 49:291–307

Kirkpatrick S, Gelatt CD, Vecchi MP (1983) Optimization by Simulated Annealing. Science 220:671–680

Krishnamurthy B (1984) An improved min-cut algonthm for partitioning vlsi networks. IEEE Transactions on computers 33(5):438–446

Krupnova H (2005) “Mapping multi-million gate socs on fpgas: industrial methodology and experience,” in Design, Automation and Test in Europe Conference and Exhibition, Proceedings, vol. 2, Feb 2004, pp. 1236–1241 Vol.2

Kuon JRI (2010) Quantifying and Exploring the Gap Between FPGAs and ASICs, Springer, Ed. Springer US, vol. 1

Kulmala A, Salminen E, and Hämäläinen TD (2007) “Evaluating large system-on-chip on multi-fpga platform,” in International Workshop on Embedded Computer Systems. Springer, pp. 179–189

M. Graphics (2018) The weather report: 2018 study on ic/asic verification trends, https://semiengineering.com/the-weather-report-2018-study-on-ic-asic-verification-trends/

M. Graphics (2020) https://www.mentor.com/products/fv/modelsim/

Marrakchi Z, Mrabet H, and Mehrez H (2005) “Hierarchical FPGA Clustering to Improve Routability,” Conference on Ph.D Research in Microelectronics and Electronics, PRIME

Marrakchi Z, Mrabet H, Mehrez H (2006) A new Multilevel Hierarchical MFPGA and its suitable configuration tools. Proc, ISVLSI, Karlsruhe, Germany

McMurchie L, Ebeling C (1995) “Pathfinder: A negotiation-based performance-driven router for fpgas,” in ACM International Symposium on Field-Programmable Gate Arrays. ACM Press, New York, NY, USA, pp. 111–117

Mehta AB (2018) Asic/soc functional design verification. Publ, Springer

Mentor graphics vista (2020) https://www.mentor.com/products/fv/vista

Patil S, Scholten S, Tao M, Al-Asaad H, Survey of memory, timing, and power management verification methods for multi-core processors, in, (2019) IEEE 10th Annual Information Technology, Electronics and Mobile Communication Conference (IEMCON). IEEE 2019:0110–0119

Pentium (1994) https://en.wikipedia.org/wiki/pentium_fdiv_bug

ProDesign (2020) https://www.profpga.com/

S2c multi-fpga prototyping (2020) http://www.s2cinc.com/design-classification/multi-fpga-prototyping

Santarini M (2005) Asic prototyping: Make versus buy. EDN 11

Sechen C, and Sangiovanni-Vincentelli A (1985) “The Timberwolf Placement and Routing Package,” JSSC, pp. 510–522

Selvakkumaran N, Ranjan A, Raje S, and Karypis G (2004) “Multi-resource aware partitioning algorithms for fpgas with heterogeneous resources,” in Proceedings of the 41st annual Design Automation Conference, pp. 741–746

Series CP (2020) http://www.cadence.com/products/sd/palladium_xp_series/pages/default.aspx

Sigenics: Custom asic calculator (2017) http://www.sigenics.com/page/custom-asic-cost-calculator

Sigl G, Doll K, and Johannes F (1991) “Analytical Placement: A Linear or a Quadratic Objective Function?” Design Automation Conference, pp. 427–432

Song X, Hung WN, Mishchenko A, Chrzanowska-Jeske M, Kennings A, and Coppola A (2003) “Board-level multiterminal net assignment for the partial cross-bar architecture,” IEEE Transactions on Very Large Scale Integration (VLSI) Systems, 11(3):511–514

Synopsys, Synplify premier (2020) https://www.synopsys.com/implementation-and-signoff/fpga-based-design/synplify-pro.html

Synopsys virtualizer (2020) https://www.synopsys.com/verification/virtual-prototyping/virtualizer.html

Tang Q, Mehrez H, and Tuna M (2013) “Routing algorithm for multi-fpga based systems using multi-point physical tracks,” in Rapid System Prototyping (RSP), 2013 International Symposium on, pp. 2–8

Tang Q, Tuna M, Mehrez H, “rformance comparison between multi-fpga prototyping platforms: Hardwired off-the-shelf, cabling, and custom,” in, (2014) IEEE 22nd Annual International Symposium on Field-Programmable Custom Computing Machines. IEEE 2014:125–132

Turki M, Marrakchi Z, Mehrez H, and Abid M (2013) Reconfigurable Computing: Architectures, Tools and Applications: 9th International Symposium, ARC 2013, Los Angeles, CA, USA, March 25-27, 2013. Proceedings. Berlin, Heidelberg: Springer Berlin Heidelberg, 2013, ch. Iterative Routing Algorithm of Inter-FPGA Signals for Multi-FPGA Prototyping Platform, pp. 210–217

Turki M, Mehrez H, Marrakchi Z, and Abid M (2013) “Partitioning constraints and signal routing approach for multi-fpga prototyping platform,” in 2013 International Symposium on System on Chip (SoC), pp. 1–4

Varghese J, Butts M, and Batcheller J (1993) “An efficient logic emulation system,” IEEE Transactions on Very Large Scale Integration (VLSI) Systems, vol. 1, no. 2, pp. 171–174

Vcs: A functional veriifcation solution by synopsys (2020) http://www.synopsys.com/Tools/Verification/FunctionalVerification/Pages/VCS.aspx

Veloce MG (2020) https://www.mentor.com/products/fv/emulation-systems/

VERIFIC (2020) https://www.verific.com/

Walters S (1991) Computer-aided prototyping for asic-based systems. IEEE Design & Test of Computers 8(2):4–10

Xilinx (2020) http://www.xilinx.com

Xilinx, Xst synthesis (2020) https://www.xilinx.com/products/design-tools/xst.html

Yang HH, and Wong D (2033) “Efficient network flow based min-cut balanced partitioning,” in The Best of ICCAD. Springer, pp. 521–534

Yang S (1991) Logic synthesis and optimization benchmarks user guide, version 3.0

Yarack E, and Carletta J (2000) “An evaluation of move-based multi-way partitioning algorithms,” in Proceedings 2000 International Conference on Computer Design. IEEE, pp. 363–369

Zebu-server asic emulator by synopsys (2020) http://www.synopsys.com/tools/verification/hardware-verification/emulation/Pages/default.aspx

Author information

Authors and Affiliations

Corresponding author

Additional information

Responsible Editor: V. D. Agrawal

Publisher’s Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Farooq, U., Mehrez, H. Pre-Silicon Verification Using Multi-FPGA Platforms: A Review. J Electron Test 37, 7–24 (2021). https://doi.org/10.1007/s10836-021-05929-1

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10836-021-05929-1