Abstract

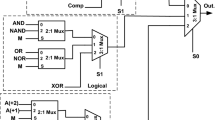

This paper proposes a carbon nanotube FET (CNFET)-based ultra-low-power dual-\(V_{DD}\) ternary half adder (HA) circuit. The proposed design utilizes both the available ternary power supply voltages (\(V_{DD}\) & \(V_{DD}/2\)) and prevents direct path between the power supplies and ground, thus significantly reducing the power dissipation as compared to the conventional designs. The performance of the proposed CNFET dual-\(V_{DD}\) HA has been compared with the same circuit implemented with 45 nm MOSFETs and also with other CNFET-based state-of-the-art HA designs proposed in the literature. The proposed HA consumes merely 86 nW of power which is significantly lesser (66–90% lower) than the power required by other ternary HA designs, and also exhibits 69–91% lower delays. The overall PDP of the proposed HA circuit is merely 4–11% of the PDP of corresponding CMOS ternary HA and other benchmarked CNFET HA designs.

Similar content being viewed by others

Data Availability Statement

All the data related to the research are included in the article. Any additional data required by any reader will be provided on request to the corresponding author.

References

N.H. Bastani, M.H. Moaiyeri, K. Navi, Circuits. Syst. Signal Process. 37(5), 1863 (2018)

J. Deng, H.P. Wong, IEEE Trans. Electron. Devices 54(12), 3186 (2007). https://doi.org/10.1109/TED.2007.909030

J. Deng, H.P. Wong, EIEEE Trans. Electron. Devices 54, 3195 (2007)

A. Doostaregan, A. Abrishamifar, Circuits Syst. Signal Process. (2020). https://doi.org/10.1007/s00034-020-01400-2

O. Hashemipour, M.H. Moaiyeri, R.F. Mirzaee, A. Doostaregan, K. Navi, IET Comput. Digit. Tech. 7(4), 167 (2013)

ITRS. International Technology Roadmap for Semiconductors. http://www.itrs2.net/ (2005)

Y. Kang, J. Kim, S. Kim, S. Shin, E. Jang, J.W. Jeong, K.R. Kim, S. Kang, in 2017 IEEE 47th International Symposium on Multiple-Valued Logic (ISMVL), pp. 25–30 (2017). https://doi.org/10.1109/ISMVL.2017.52

S. Karmakar, J.A. Chandy, F.C. Jain, IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 21(5), 793 (2013). https://doi.org/10.1109/TVLSI.2012.2198248

P. Keshavarzian, R. Sarikhani, Circuits. Syst. Signal Process. 33(3), 665 (2014)

S. Kim, T. Lim, S. Kang, in 2018 23rd Asia and South Pacific Design Automation Conference (ASP-DAC), pp. 476–481 (2018). https://doi.org/10.1109/ASPDAC.2018.8297369

S. Lin, Y. Kim, F. Lombardi, IEEE Trans. Nanotechnol. 10(2), 217 (2011). https://doi.org/10.1109/TNANO.2009.2036845

M.H. Moaiyeri, S. Sedighiani, F. Sharifi, K. Navi, Front. Inf. Technol. Electron. Eng. 17(10), 1056 (2016)

J. Mounika, K. Ramanujam, M.Z. Jahangir, in 2016 International Conference on Circuit, Power and Computing Technologies (ICCPCT), pp. 1–5 (2016). https://doi.org/10.1109/ICCPCT.2016.7530153

S.L. Murotiya, A. Gupta, Arab. J. Sci. Eng. 39(11), 7839 (2014)

S.K. Sahoo, G. Akhilesh, R. Sahoo, M. Muglikar, IEEE Trans. Nanotechnol. 16(3), 368 (2017). https://doi.org/10.1109/TNANO.2017.2649548

T. Sharma, L. Kumre, Circuits. Syst. Signal Process. 38(10), 4640 (2019)

S. Shin, J.W. Jeong, E. Jang, K.R. Kim, in 2017 IEEE 17th International Conference on Nanotechnology (IEEE-NANO), pp. 13–16 (2017). https://doi.org/10.1109/NANO.2017.8117372

B. Srinivasu, K. Sridharan, IEEE Trans. Circuits Syst. I: Reg. Pap. 64(8), 2146 (2017). https://doi.org/10.1109/TCSI.2017.2686446

S. Tabrizchi, N. Azimi, K. Navi, Front. Inf. Technol. Electron. Eng. 18(3), 423 (2017)

S. Vidhyadharan, R. Ramakant, A.S. Vidhyadharan, A.K. Shyam, M.P. Hirpara, S.S. Dan, in 2019 32nd International Conference on VLSI Design and 2019 18th International Conference on Embedded Systems (VLSID), pp. 401–406 (2019). https://doi.org/10.1109/VLSID.2019.00087

S. Vidhyadharan, R. Yadav, G. Akhilesh, V. Gupta, A. Ravi, S.S. Dan, in The Physics of Semiconductor Devices, ed. by R.K. Sharma, D. Rawal (Springer International Publishing, 2019), pp. 619–628

S. Vidhyadharan, R. Yadav, S. Hariprasad, S.S. Dan, Analog Integrated Circuits and Signal Processing (2019)

S. Vidhyadharan, R. Yadav, S. Hariprasad, S.S. Dan, Springer Analog Integrated Circuits & Signal Processing (2019). https://doi.org/10.1007/s10470-019-01487-x

C.K. Vudadha, M. Srinivas, in 2018 IEEE 48th International Symposium on Multiple-Valued Logic (ISMVL), pp. 192–197 (2018). https://doi.org/10.1109/ISMVL.2018.00041. ISSN: 2378-2226

C. Vudadha, A. Surya, S. Agrawal, M.B. Srinivas, IEEE Trans. Circuits Syst. I: Reg. Pap. 65(12), 4313 (2018)

Author information

Authors and Affiliations

Corresponding author

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Vidhyadharan, A.S., Bha, K. & Vidhyadharan, S. CNFET-Based Ultra-Low-Power Dual-\(V_{DD}\) Ternary Half Adder. Circuits Syst Signal Process 40, 4089–4105 (2021). https://doi.org/10.1007/s00034-021-01664-2

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s00034-021-01664-2