Abstract

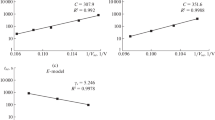

A gate dielectric is one of the key structural elements of submicron MOS transistors, on which the reliability of its operation depends. A breakdown of the dielectric leads to a loss in the functioning of the transistor and the failure of the entire IC or a malfunction in its operation. Therefore, special attention is paid to assess the defectiveness of a gate dielectric and its operating time to failure. In this study, the operating time to failure of the gate insulator of MOS transistors is determined based on the method of the time-dependent breakdown of the dielectric using the thermomechanical model (E models). The Weibull distribution obtained for the integrated failure distribution of a sample of technological test structures measured at high voltage and temperature is used as the statistics of the distribution of failures. The studies are performed on the test structures, which are MOS capacitors with the gate dielectric thickness of 5 nm. The test structures are created using the 65 nm serial technology and are placed in a test crystal together with the IC on one plate. Software is developed that allows accelerated measurements in the automatic mode. As a result of the studies, the parameters of the thermomechanical failure model are determined, and the dependences of the operating time to failure of the gate dielectric on the operating conditions are obtained. It is established that for the test structures under study, both full and partial breakdown of the dielectric can occur. This control method can be used to predict the long-term reliability of the gate dielectric of sub-100-nm MOS transistors and certify the technological processes of its production.

Similar content being viewed by others

REFERENCES

Jedec Standart JEP001-2A: Foundry process qualification guidelines—front end transistor level, 2018.

Stathis, J.H., Linder, B.P., Rodríguez, R., and Lombardo, S., Reliability of ultra-thin oxides in CMOS circuits, Microelectron. Reliab., 2003, vol. 43, nos. 9–11, pp. 1353–1360.

Benediktov, A.S., Ignatov, P.V., Mikhailov, A.A., and Potupchik, A.G., Reliability investigation of 0.18-μm SOI MOS transistors at high temperatures, Russ. Microelectron., 2018, vol. 47, no. 5, pp. 317–322.

Solodukha, V.A., Pilipenko, V.A., Chigir’ G.G., et al., Reliability express control of the gate dielectric of semiconductor devices, Prib. Metody Izmeren., 2018, vol. 9, no. 4, pp. 306–313. https://doi.org/10.21122/2220-9506-2018-9-4-306-313

Sivchenko, A.S., Method for determining the defectiveness of a gate dielectric using accelerated testing of test structures, Izv. Vyssh. Uchebn. Zaved., Elektron., 2015, vol. 20, no. 3, pp. 304–312.

Sivchenko, A.S., Development of a technique for analyzing the defectiveness of a gate dielectric on test structures in plates, in Problemy razrabotki perspektivnykh mikro- i nanoelektronnykh sistem: sb. tr (Problems of Developing Promising Micro- and Nanoelectronic Systems, Collection of Articles), Stempkovskii, A.L., Ed., Moscow: IPPM RAN, 2014, part 2, pp. 145–150.

Dumin, D.J., Oxide Reliability: A Summer of Silicon Oxide Wearout, Breakdown and Reliability, Singapore: World Scientific, 2002.

Sahhaf, R. and Degraeve, Ph.J., Roussel, Ph.J., et al., TDDB reliability prediction based on the statistical analysis of hard breakdown including multiple soft breakdown and wear-out, in Proceedings of the 2007 IEEE International Electron Devices Meeting, 2007, pp. 501–504.

Martin, A., von Hagen, J., and Alers, G.B., Ramped current stress for fast and reliable wafer level reliability monitoring of thin gate oxide reliability, Microelectron. Reliab., 2003, vol. 43, pp. 1215–1220.

McPherson, J.W., Time dependent dielectric breakdown physics—models revisited, Microelectron. Reliab., 2012, vol. 52, nos. 9–10, pp. 1753–1760.

Jedec Standart JESD 92: Procedure for characterizing time depend dielectric breakdown of ultra-thin gate dielectrics, 2003.

Author information

Authors and Affiliations

Corresponding author

Ethics declarations

The study was performed on the equipment of the Scientific-Manufacturing Complex “Technological Centre.”

Rights and permissions

About this article

Cite this article

Sivchenko, A.S., Kuznetsov, E.V. & Saurov, A.N. Determination of the Operating Time to Failure of a Sub-100-nm MOS Transistor Gate Dielectric Using Accelerated Tests. Russ Microelectron 49, 479–484 (2020). https://doi.org/10.1134/S1063739720070124

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1134/S1063739720070124