Abstract

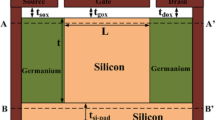

While scaling down the devices it is important not to compromise with the performance. Scaling of tunnel devices shows better performance than Field Effect Transistors (FETs). Charge Plasma based Dopingless Double Gate Tunnel Field Effect Transistor (DLDGTFET) with its various misaligned configurations are designed, discussed and analyzed in the presented work. Silicon is preferred as a choice of material. For various misalignment configurations, initially, bottom gate is shifted towards the right, then it is shifted towards left and at last bottom and top, both gates are misplaced for analyzing the device parameters, analog parameters and linearity parameters. By misalignment, it is observed that either the bottom gate is misaligned towards the right or left or both gates are being misaligned, device performance degraded. The basic structure shows the higher drain current, better drive current among other structures such as 15 μA. whereas source underlapped (SU100) structure shows the better subthreshold slope such as 20 mV/decade. But SU100 has the least amount of drive current. In the subthreshold region, BM100 has the maximum value of transconductance gain factor i.e. 104 V−1. When the bottom gate is shifted towards right i.e. for drain overlapped structure it was observed that it shows better linearity parameters and can be considered for low noise and low voltage applications.

Similar content being viewed by others

Data Availability

Not Applicable.

References

Han K, Long S, Deng Z, Zhang Y, Li J (2020) A novel germanium-around-source gate-all-around tunnelling field-effect transistor for low-power applications. Micromachines 11(2):164. https://doi.org/10.3390/mi11020164

Young KK (1989) Short-channel effect in fully depleted SOI MOSFETs. IEEE Trans Electron Devices 36(2):399–402. https://doi.org/10.1109/16.19942

Huang X, Lee WC, Kuo C, Hisamoto D, Chang L, Kedzierski J, Anderson E, Takeuchi H, Choi YK, Asano K, Subramanian V (2001) Sub-50 nm P-channel FinFET. IEEE Trans Electron Devices 48(5):880–886. https://doi.org/10.1109/16.918235

Yadav S, Sharma D, Chandan BV, Aslam M, Soni D, Sharma N (2018) A novel hetero-material gate-underlap electrically doped TFET for improving DC/RF and ambipolar behaviour. Superlattice Microst 117:9–17. https://doi.org/10.1016/j.spmi.2018.02.005

Bangsaruntip S, Cohen GM, Majumdar A, Sleight JW (2010) Universality of short-channel effects in undoped-body silicon nanowire MOSFETs. IEEE Electron Device Lett 31(9):903–905. https://doi.org/10.1109/LED.2010.2052231

Saurabh S, Kumar MJ Fundamental of tunnel field effect transistors

Boucart K, Ionescu AM (2007) Double-gate tunnel FET with high-k gate dielectric. IEEE Trans Electron Devices 54(7):1725–1733. https://doi.org/10.1109/TED.2007.899389

Musalgaonkar G, Sahay S, Saxena RS, Kumar MJ (2019) Nanotube Tunneling FET with a Core source for Ultrasteep subthreshold swing: a simulation study. IEEE Trans Electron Devices 66(10):4425–4432. https://doi.org/10.1109/TED.2019.2933756

Wu C, Huang Q, Zhao Y, Wang J, Wang Y, Huang R (2016) A novel tunnel FET design with stacked source configuration for average subthreshold swing reduction. IEEE Trans Electron Devices 63(12):5072–5076. https://doi.org/10.1109/TED.2016.2619694

Beohar A, Vishvakarma SK (2016) Performance enhancement of asymmetrical underlap 3D-cylindrical GAA-TFET with low spacer width. Micro Nano Lett 11(8):443–445. https://doi.org/10.1049/mnl.2016.0202

Singh S, Raman A, Kumar N (2017) Design and optimization analysis of dual material gate on DG-IMOS. J Semiconduct 38(12):124003

Gopalakrishnan K, Griffin PB, Plummer JD (2004) Impact ionization MOS (I-MOS)-part I: device and circuit simulations. IEEE Trans Electron Devices 52(1):69–76. https://doi.org/10.1109/TED.2004.841344

Musalgaonkar G, Sahay S, Saxena RS, Kumar MJ (2018) An impact ionization MOSFET with reduced breakdown voltage based on back-gate misalignment. IEEE Trans Electron Devices 66(2):868–875. https://doi.org/10.1109/TED.2018.2887168

Onal C, Woo R, Koh HYS, Griffin PB, Plummer JD (2008) A novel depletion-IMOS (DIMOS) device with improved reliability and reduced operating voltage. IEEE Electron Device lett 30(1):64–67. https://doi.org/10.1109/LED.2008.2008029

Yadav S, Sharma D, Soni D, Aslam M (2017) Controlling ambipolarity with improved RF performance by drain/gate work function engineering and using high k-dielectric material in electrically doped TFET: proposal and optimization. J Comput Electron 16(3):721–731. https://doi.org/10.1007/s10825-017-1019-2

Ionescu AM, Riel H (2011) Tunnel field-effect transistors as energy-efficient electronic switches. Nature, 479(7373), pp.329-337. https://doi.org/10.1038/nature10679

Choi WY, Park BG, Lee JD, Liu TJK (2007) Tunneling field-effect transistors (TFETs) with subthreshold swing (SS) less than 60 mV/dec. IEEE Electron Device Lett 28(8):743–745. https://doi.org/10.1109/LED.2007.901273

Kumar N, Raman A (2019) Design and investigation of charge-plasma-based work function engineered dual-metal-heterogeneous gate Si-Si 0.55 Ge 0.45 GAA-cylindrical NWTFET for ambipolar analysis. IEEE Trans Electron Devices 66(3):1468–1474. https://doi.org/10.1109/TED.2019.2893224

Singh S, Raman A (2018) A dopingless gate-all-around (GAA) gate-stacked nanowire FET with reduced parametric fluctuation effects. J Comput Electron 17(3):967–976. https://doi.org/10.1007/s10825-018-1166-0

Damrongplasit N, Shin C, Kim SH, Vega RA, Liu TJK (2011) Study of random dopant fluctuation effects in germanium-source tunnel FETs. IEEE Trans Electron Devices 58(10):3541–3548. https://doi.org/10.1109/TED.2011.2161990

Chiang MH, Lin JN, Kim K, Chuang CT (2007) Random dopant fluctuation in limited-width FinFET technologies. IEEE Trans Electron Devices 54(8):2055–2060. https://doi.org/10.1109/TED.2007.901154

Jhaveri R, Nagavarapu V, Woo JC (2010) Effect of pocket doping and annealing schemes on the source-pocket tunnel field-effect transistor. IEEE Trans Electron Devices 58(1):80–86. https://doi.org/10.1109/TED.2010.2089525

Damrongplasit N, Kim SH, Liu TJK (2013) Study of random dopant fluctuation induced variability in the raised-Ge-source TFET. IEEE electron Device Lett 34(2):184–186. https://doi.org/10.1109/LED.2012.2235404

Lahgere A, Sahu C, Singh J (2015) Electrically doped dynamically configurable field-effect transistor for low-power and high-performance applications. Electron Lett 51(16):1284–1286. https://doi.org/10.1049/el.2015.0079

Nigam K, Kondekar P, Sharma D (2016) DC characteristics and analog/RF performance of novel polarity control GaAs-Ge based tunnel field effect transistor. Superlattice Microst 92:224–231. https://doi.org/10.1016/j.spmi.2016.01.032

Kumar M, Jit S (2015) Effects of electrostatically doped source/drain and ferroelectric gate oxide on subthreshold swing and impact ionization rate of strained-Si-on-insulator tunnel field-effect transistors. IEEE Trans Nanotechnol 14(4):597–599. https://doi.org/10.1109/TNANO.2015.2426316

Kumar N, Raman A (2019) Low voltage charge-plasma based dopingless tunnel field effect transistor: analysis and optimization. Microsystem Technol:1-8. https://doi.org/10.1007/s00542-019-04666-y

Anand S, Sarin RK (2018) Hetero-material gate doping-less tunnel FET and its misalignment effects on Analog/RF parameters. J Electron Mater 47(5):2988–2996. https://doi.org/10.1007/s11664-018-6174-0

Ghosh B, Akram MW (2013) Junctionless tunnel field effect transistor. IEEE Electron Device Lett 34(5):584–586. https://doi.org/10.1109/LED.2013.2253752

Amin SI, Sarin RK (2015) Analog performance investigation of misaligned double gate junctionless transistor. J Comput Electron 14(3):675–685. https://doi.org/10.1007/s10825-015-0705-1

Gundapaneni S, Bajaj M, Pandey RK, Murali KV, Ganguly S, Kottantharayil A (2012) Effect of band-to-band tunneling on junctionless transistors. IEEE Trans Electron Devices 59(4):1023–1029. https://doi.org/10.1109/TED.2012.2185800

Moselund KE, Schmid H, Bessire C, Bjork MT, Ghoneim H, Riel H (2012) InAs–Si nanowire heterojunction tunnel FETs. IEEE Electron Device Lett 33(10):1453–1455. https://doi.org/10.1109/LED.2012.2206789

Lee K, Lee J, Kim S, Park E, Lee R, Kim HM, Kim S, Park BG (2019) Tunnel field effect transistor with ferroelectric gate insulator. J Nanosci Nanotechnol 19(10):6095–6098. https://doi.org/10.1166/jnn.2019.16994

Kumar N, Mushtaq U, Amin SI, Anand S (2019) Design and performance analysis of dual-gate all around core-shell nanotube TFET. Superlattice Microst 125:356–364. https://doi.org/10.1016/j.spmi.2018.09.012

Yin C, Chan PC (2004) Investigation of the source/drain asymmetric effects due to gate misalignment in planar double-gate MOSFETs. IEEE Trans Electron Devices 52(1):85–90. https://doi.org/10.1109/TED.2004.841349

Anand S, Sarin RK (2017) Gate misalignment effects on analog/RF performance of charge plasma-based doping-less tunnel FET. Appl Phys A 123(6):413. https://doi.org/10.1007/s00339-017-1029-8

Shekhar D, Raman A (2020) Design and analysis of dual-gate misalignment on the performance of dopingless tunnel field effect transistor. Appl Phys A 126:441. https://doi.org/10.1007/s00339-020-03615-1

Manual, ATLAS User’S (2010). Silvaco. Santa Clara, CA

Kim JH, Kim S, Park BG (2019) Double-gate TFET with vertical channel sandwiched by lightly doped Si. IEEE Trans Electron Devices 66(4):1656–1661. https://doi.org/10.1109/TED.2019.2899206

Kumar MJ, Janardhanan S (2013) Doping-less tunnel field effect transistor: design and investigation. IEEE Trans Electron Devices 60(10):3285–3290. https://doi.org/10.1109/TED.2013.2276888

Luisier M, Klimeck G (2010) Simulation of nanowire tunneling transistors: from the Wentzel–Kramers–Brillouin approximation to full-band phonon-assisted tunneling. J Appl Phys 107(8):084507. https://doi.org/10.1063/1.3386521

Kumar N, Raman A (2019) Performance assessment of the charge-plasma-based cylindrical GAA vertical nanowire TFET with impact of interface trap charges. IEEE Trans Electron Devices 66(10):4453–4460. https://doi.org/10.1109/TED.2019.2935342

Chandan BV, Dasari S, Yadav S, Sharma D (2018) Approach to suppress ambipolarity and improve RF and linearity performances on ED-tunnel FET. Micro Nano Lett 13(5):684–689. https://doi.org/10.1049/mnl.2017.0814

Biswal SM, Baral B, De D, Sarkar A (2016) Study of effect of gate-length downscaling on the analog/RF performance and linearity investigation of InAs-based nanowire tunnel FET. Superlattice Microst 91:319–330. https://doi.org/10.1016/j.spmi.2016.01.021

Gupta AK, Raman A, Kumar N (2019) Design and investigation of a novel charge plasma-based core-shell ring-TFET: analog and linearity analysis. IEEE Trans Electron Devices 66(8):3506–3512. https://doi.org/10.1109/TED.2019.2924809

Gupta AK, Raman A (2020) Electrostatic-doped nanotube TFET: proposal, design, and investigation with linearity analysis. Silicon. https://doi.org/10.1007/s12633-020-00584-1

Acknowledgments

The Author wishes to thanks Dr. Ashish Raman for his work in the field of semiconductor devices. We also thanks to the VLSI design Lab., Department of Electronics and communications, Dr. B. R. Ambedkar National Institute of Technology, Jalandhar, 144011, India.

Funding

No funding was received for conducting this study.

Author information

Authors and Affiliations

Contributions

All the authors contributed to the study conception and design, literature review, material preparation, simulation, and analysis were performed by [Deep Shekhar] and [Dr. Ashish Raman]. The final draft of the manuscript was written by [Deep Shekhar] and all authors commented on the previous version of the manuscripts. All authors read and approved the final manuscript.

Corresponding author

Ethics declarations

No funding was received for conducting this study. Informed consent was obtained from all individual participants included in the study. The authors report no conflicts of interest. This article does not contain any studies with human or animal subjects.

Conflict of Interest

The authors whose names are listed immediately below certify that they have NO affiliations with or involvement in any organization or entity with any financial interest (such as honour-aria; educational grants; participation in speakers’ bureaus; membership, employment, consultancies, stock ownership, or other equity interest; and expert testimony or patent-licensing arrangements), or non-financial interest (such as personal or professional relationships, affiliations, knowledge or beliefs) in the subject matter or materials discussed in this manuscript.

Consent to Participate

Authors voluntarily agreed to participate in the research.

Consent for Publication

The Author transfers to Springer the non-exclusive publication rights and he warrants that his contribution is original and that he has full power to make this grant. The author signs for and accepts responsibility for releasing this material on behalf of all co-authors. This transfer of publication rights covers the non-exclusive right to reproduce and distribute the article, including reprints, translations, photographic reproductions, microform, electronic form (offline, online) or any other reproductions of similar nature.

Additional information

Publisher’s Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Shekhar, D., Raman, A. Tweaking the Performance of Dopingless Nano-TFET with Misaligned Sandwiched Dual-Gate Structure. Silicon 13, 3713–3723 (2021). https://doi.org/10.1007/s12633-021-00956-1

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s12633-021-00956-1