Abstract

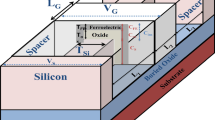

CMOS scaling is the approach to accomplish the VLSI goals in the past decades. The existing CMOS technology is facing challenges related to short channel effects and reached to its performance limits at sub-10 nm technology nodes. The negative capacitance field-effect transistor is a potential device for near future technology to overcome these challenges. In the present work, negative capacitance Junctionless (NC-JL) FinFET with Metal-Ferroelectric–Insulator-Semiconductor (MFIS) structure is proposed and analysed comprehensively using TCAD simulation for its scaling capability over the various technology nodes starting from 24 nm to 5 nm. It is revealed that the integration of negative capacitance (NC) with JL FinFET helps to reduce the leakage current, short channel effects such as subthreshold slope, DIBL and provide high drive current as well as fast switching by reducing intrinsic delay for extremely short channel length as compared to standard-JL FinFET. Furthermore, the different performance parameters including Gate Induced Drain Leakage Current (GIDL) of proposed NC-JL FinFET are comprehensively studied.

Similar content being viewed by others

Data Availability

Not Applicable.

References

Ieong M (2004) Silicon device scaling to the Sub-10-nm regime. Science 306:2057–2060. https://doi.org/10.1126/science.1100731

Chen S, Shang E, Hu S (2018) Gate length scaling optimization of FinFETs. Int J Mod Phys B 32:1850176. https://doi.org/10.1142/s021797921850176x

Razavieh A, Zeitzoff P, Nowak EJ (2019) Challenges and limitations of CMOS scaling for FinFET and beyond architectures. IEEE Trans Nanotechnol 18:999–1004. https://doi.org/10.1109/tnano.2019.2942456

Colinge J-P, Lee C-W, Afzalian A, Akhavan ND, Yan R, Ferain I, Razavi P, O’Neill B, Blake A, White M, Kelleher A-M, McCarthy B, Murphy R (2010) Nanowire transistors without junctions. Nat Nanotechnol 5:225–229. https://doi.org/10.1038/nnano.2010.15

Ionescu AM (2010) Nanowire transistors made easy. Nat Nanotechnol 5:178–179. https://doi.org/10.1038/nnano.2010.38

Kumar K, Raman A, Raj B, Singh S, Kumar N (2020) Design and optimization of junctionless-based devices with noise reduction for ultra-high frequency applications. Appl Phys A Mater Sci Process 126:1–11. https://doi.org/10.1007/s00339-020-04092-2

Aggarwal A, Raman A, Kumar N, Singh S (2019) Nanocantilever tri-gate junctionless cuboidal nanowire-FET-based directional pressure sensor. Appl Phys A 125:125. https://doi.org/10.1007/s00339-019-2670-1

Yu HY, Ren C, Yeo Y-C, Kang JF, Wang XP, Ma HHH, Li M-F, Chan DSH, Kwong D-L (2004) Fermi pinning-induced thermal instability of metal-gate work functions. IEEE Electron Device Lett 25:337–339. https://doi.org/10.1109/led.2004.827643

Rathore RS, Rana AK (2017) Investigation of metal-gate work-function variability in FinFET structures and implications for SRAM cell design. Superlattice Microst 110:68–81. https://doi.org/10.1016/j.spmi.2017.09.003

Salahuddin S, Datta S (2008) Use of negative capacitance to provide voltage amplification for low power nanoscale devices. Nano Lett 8:405–410. https://doi.org/10.1021/nl071804g

Khan AI, Chatterjee K, Wang B, Drapcho S, You L, Serrao C, Bakaul SR, Ramesh R, Salahuddin S (2014) Negative capacitance in a ferroelectric capacitor. Nature Mater 14:182–186. https://doi.org/10.1038/nmat4148

Pahwa G, Agarwal A, Chauhan YS (2018) Numerical investigation of Short-Channel effects in negative capacitance MFIS and MFMIS transistors: subthreshold behavior. IEEE Trans Electron Devices 65:5130–5136. https://doi.org/10.1109/ted.2018.2870519

Gupta AK, Raman A, Kumar N (2020) Charge-plasma-based negative capacitance ring-FET: design, investigation and reliability analysis. J Electron Mater 49:4852–4863. https://doi.org/10.1007/s11664-020-08205-8

ITRS 2.0 (2013) International Technology Roadmap for Semiconductors. http://www.itrs2.net. Accessed Jul 2020

Sentaurus TCAD Synopsys (2017) Synopsys. https://www.synopsys.com

Choi S-J, Moon D-I, Kim S, Duarte JP, Choi Y-K (2011) Sensitivity of threshold voltage to nanowire width variation in junctionless transistors. IEEE Electron Device Lett 32:125–127. https://doi.org/10.1109/led.2010.2093506

Kaundal S, Rana AK (2018) Design and structural optimization of junctionless FinFET with Gaussian-doped channel. J Comput Electron 17:637–645. https://doi.org/10.1007/s10825-018-1131-y

Jiang C, Liang R, Wang J, Xu J (2016) Simulation-based study of negative capacitance double-gate junctionless transistors with ferroelectric gate dielectric. Solid State Electron 126:130–135. https://doi.org/10.1016/j.sse.2016.09.001

Li J, Li Y, Zhou N, Xiong W, Wang G, Zhang Q, Du A, Gao J, Kong Z, Lin H, Xiang J (2020) Study of silicon nitride inner spacer formation in process of gate-all-around nano-transistors. Nanomaterials 10:793. https://doi.org/10.3390/nano10040793

Koehler F, Triyoso DH, Hussain I, Antonioli B, Hempel K (2014) Challenges in spacer process development for leading-edge high-k metal gate technology. Phys Status Solidi (C) 11:73–76. https://doi.org/10.1002/pssc.201300157

Mehta H, Kaur H (2018) Impact of Gaussian doping profile and negative capacitance effect on double-gate Junctionless transistors (DGJLTs). IEEE Trans Electron Devices 65:2699–2706. https://doi.org/10.1109/ted.2018.2832843

Yang T, Hu J, Ni H (2019) Negative capacitance independent multi-gate FinFETs and their optimisations. Int J Electron 106:1229–1247. https://doi.org/10.1080/00207217.2019.1584918

Iwai H (2009) Technology roadmap for 22nm and beyond. In: 2009 2nd international workshop on electron devices and semiconductor technology. IEEE https://doi.org/10.1109/ted.2020.2967463

Kaundal S, Rana AK (2018) Physical insights on scaling of Gaussian channel design junctionless FinFET. J Nanoelectron Optoelectron 13:653–660. https://doi.org/10.1166/jno.2018.2301

Amrouch H, Pahwa G, Gaidhane AD, Henkel J, Chauhan YS (2018) Negative capacitance transistor to address the fundamental limitations in technology scaling: processor performance. IEEE Access 6:52754–52765. https://doi.org/10.1109/access.2018.2870916

Sahay S, Kumar MJ (2017) Physical insights into the nature of gate-induced drain leakage in Ultrashort Channel nanowire FETs. IEEE Trans Electron Devices 64:2604–2610. https://doi.org/10.1109/ted.2017.2688134

Sahay S, Kumar MJ (2016) Insight into lateral band-to-band-tunneling in nanowire junctionless FETs. IEEE Trans Electron Devices 63:4138–4142. https://doi.org/10.1109/ted.2016.2601239

Sahay S, Kumar MJ (2017) Diameter dependence of leakage current in nanowire junctionless field effect transistors. IEEE Trans Electron Devices 64:1330–1335. https://doi.org/10.1109/ted.2016.2645640

Acknowledgements

The authors would like to thank the Department of Electronics and Communication Engineering, National Institute of Technology, Hamirpur, Himachal Pradesh, India for providing valuable support to carry out this study in VLSI & Nano Laboratory.

Author information

Authors and Affiliations

Contributions

Design, Methodology, Formal analysis, and investigation, Validation, Writing - original draft preparation: [Shelja Kaushal]; Conceptualization, Resources, Supervision: [Ashwani K. Rana]; Writing - review and editing: [Rajneesh Sharma].

Corresponding author

Ethics declarations

Conflicts of Interest/Competing Interests

The authors have no relevant financial or non-financial interests to disclose.

Ethics Approval and Consent to Participate

Not Applicable.

Consent for Publication

Not Applicable.

Code Availability

Not Applicable.

Additional information

Publisher’s Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Kaushal, S., Rana, A.K. & Sharma, R. Performance Evaluation of Negative Capacitance Junctionless FinFET under Extreme Length Scaling. Silicon 13, 3681–3690 (2021). https://doi.org/10.1007/s12633-020-00931-2

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s12633-020-00931-2