Abstract

In this paper, a CMOS based precharged phase frequency detector (PPFD) with improved output characteristic for phase locked loop (PLL) has been proposed and analyzed. The proposed PFD minimizes the reset time to improve the output characteristics and works upto the frequency of 1.25 MHz–3.8 GHz. In addition, it has an advantage of precharged PFD which has low power consumption capability i.e., 285.77 \(\upmu\) w. The design is based on standard 0.18 \(\upmu\) m CMOS process technology with the supply voltage of 1.8 V and achieves phase noise of \(-135.45\) dBc/Hz at 1 MHz offset. Further, the proposed design has minimized the Blind zone to 63 ps and has completely eliminated the dead zone in the phase characteristics. This is required for low noise phase locked loop (PLL) application.

Similar content being viewed by others

Notes

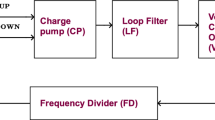

Charge pump is the block used after the PFD in the PLL block.

References

Chen, O. T. C., & Sheen, R. R.-B. (2002). A power-efficient wide-range phase-locked loop. IEEE Journal of Solid-State Circuits, 37(1), 51–62.

Razavi, B. (2002). Design of analog CMOS integrated circuits. Chennai: Tata McGraw-Hill Education.

Chiu, W. H., Huang, Y. H., & Lin, T. H. (2010). A dynamic phase error compensation technique for fast-locking phase-locked loops. IEEE Journal of Solid-State Circuits, 11(6), 1137–1149.

Tang, Y., & Geiger, R. L. (2002). Phase detector for PLL-based high-speed data recovery. Electronics Letters, 38(23), 1417–1419.

Kumar, N., & Kumar, M. (2016). Design of low power and high speed phase detector. In 2016 2nd International Conference on Contemporary Computing and Informatics (IC3I), pp 676–680.

Mansuri, M., Liu, D., & Yang, C. K. K. (2001). Fast frequency acquisition phase-frequency detectors for GSa/s phase-locked loops. In Proceedings of the 27th European Solid-State Circuits Conference, pp 333–336.

Charles, C. T., & Allstot, D. J. (2006). A calibrated phase/frequency detector for reference spur reduction in charge-pump PLLs. IEEE Transactions on Circuits and Systems II: Express Briefs, 53(9), 822–826.

Nanda, U., Acharya, D. P., & Patra, S. K. (2017). Design of an efficient phase frequency detector to reduce blind zone in a PLL. Microsystem Technologies, 23(3), 533–539.

Homayoun, A., & Razavi, B. (2013). Analysis of phase noise in phase/frequency detectors. IEEE Transactions on Circuits and Systems I: Regular Papers, 60(3), 529–539.

Chou, C. P., Lin, Z. M., & Chen, J. D. (2004). A 3-ps dead-zone double-edge-checking phase-frequency-detector with 4.78 GHz operating frequencies. In The 2004 IEEE Asia-Pacific Conference on Circuits and Systems, 2004. Proceedings, 2, pp 937–940.

Hu, W., Chunglen, L., & Wang, X. (2007). Fast frequency acquisition phase-frequency detector with zero blind zone in PLL. Electronics Letters, 43(19), 1018–1020.

Tak, G. Y., Hyun, S. B., Kang, T. Y., Choi, B. G., & Park, S. S. (2005). A 6.3–9-GHz CMOS fast settling PLL for MB-OFDM UWB applications. IEEE Journal of Solid-State Circuit, 40(8), 1671–1679.

Chen, W. H., Inerowicz, M. E., & Jung, B. (2010). Phase frequency detector with minimal blind zone for fast frequency acquisition. IEEE Transactions on Circuits and Systems II: Express Briefs, 57(12), 936–940.

Brennan, P. V., & Thompson, I. (2001). Phase/frequency detector phase noise contribution in PLL frequency synthesiser. Electronics letters, 37(15), 939–940.

Gao, X., Klumperink, E. A. M., Bohsali, M., & Nauta, B. (2009). A low noise sub-sampling PLL in which divider noise is eliminated and PD/CP noise is not multiplied by \(N^{2}\). IEEE Journal of Solid-State Circuits, 44(12), 3253–3263.

Chen, R. Y., & Yang, Z. Y. (2010). Modeling the high-frequency degradation of phase/frequency detectors. IEEE Transactions on Circuits and Systems II: Express Briefs, 57(5), 394–398.

Majeed, K. K. A., & Kailath, B. J. (2013). A novel phase frequency detector for a high frequency PLL design. Procedia Engineering, 64, 377–384.

Johnson, T., Fard, A., & Aberg, D. (2004). An improved low voltage phase-frequency detector with extended frequency capability. In The 2004 47th Midwest Symposium on Circuits and Systems, 2004. MWSCAS’04, 1, pp I–181.

Acknowledgements

Authors would like to thank, Ministry of Electronics and Information Technology (MeitY) Govt. of India for providing financial support under SMDP-C2SD Project.

Author information

Authors and Affiliations

Corresponding author

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Pradhan, N., Jana, S.K. Design of phase frequency detector with improved output characteristics operating in the range of 1.25 MHz–3.8 GHz. Analog Integr Circ Sig Process 107, 101–108 (2021). https://doi.org/10.1007/s10470-020-01779-7

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10470-020-01779-7