Abstract

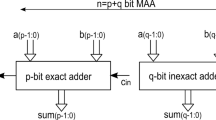

In this paper, approximate adders were proposed for DSP processors. DSP processors are mainly composed of adders and multipliers at bottom level. The power is minimized in transistor level design. Proposed adders have less power dissipation when compared to existing approximate adders. Results have shown that the proposed adders have less PDP with more accuracy. The circuits were simulated in Cadence virtuoso tool under 45 nm CMOS technology. Supply voltage is + 0.5 V.

Similar content being viewed by others

References

Pashaeifar, M., Kamal, M., & Afzali-Kusha, A. (2018). Approximate reverse carry propagate adder for energy-efficient DSP applications. IEEE Trans Very Large Scale Integr Syst (VLSI), 26(11), 2530–2541.

Yang, Z., Han, J., Lombardi, F. (2015). Transmission gate-based approximate adders for inexact computing. In: Proc. IEEE/ACM Int. Symp. Nanosc. Archit. (NANOARCH) pp. 145–150.

Gupta, V., Mohapatra, D., Raghunathan, A., & Roy, A. (2013). Low-power digital signal processing using approximate adders. IEEE Trans Compuer-Aided Design Integr Circuits Syst, 32(11), 24–137.

Zhu, N., Goh, W. L., Zhang, W., Yeo, K. S., & Kong, Z. H. (2009). Design of low-power high-speed truncation-error-tolerant adder and its application in digital signal processing. IEEE Transactions on Very Large Scale Integration (VLSI) Systems, 18(8), 1225–1229.

Yang, Z., Jain, A., Liang, J., Han, J., & Lombardi, F. (2013).Approximate XOR/XNOR- based adders for inexact computing. In: 2013 13th Proceedings of International Conference on Nanotechnology (NANO), (pp. 690–693). IEEE.

Kung, D., Kim, J., & Mukhopadhyay, S. (2015). On the impact of energy- accuracy tradeoff in a digital cellular neural network for image processing. IEEE Transactions Computer Aided Design of Integrated Circuits and Systems, 34(7), 1070–1081.

Madanayake, A., Cintra, R. J., Dimitrov, V., Bayer, F., Wahid, K. A., Kulasekera, S., et al. (2015). Low-power VLSI architectures for DCT/DWT: precision vs Approximation for HD video, biomedical, and smart antenna applications. IEEE Circuits and Systems Magazine, 15(1), 25–47.

Ghosh, S., Mohapatra, D., Karakonstantis, G., & Roy, K. (Sep. 2010). Voltage scalable high-speed robust hybrid arithmetic units using adaptive clocking. IEEE Transactions Very Large Scale Integrations (VLSI) Systems, 18(9), 1301–1309.

Jiang, H., Liu, C., Lombardi, F., & Han, J. (2019). Low-power approximate unsigned multipliers with configurable error recovery. IEEE Transactions on Circuits and Systems I: Regular Papers, 66(1), 189–202.

Han, J., Chen, H., Liang, J., Zhu, P., Yang, Z., & Lombardi, F. (2014). A stochastic computational approach for accurate and efficient reliability evaluation. IEEE Transactions on Computers, 63(6), 1336–1350.

Chen, H., Han, J. & Lombardi, F. (2011). A Transistor-Level Stochastic Approach for Evaluating the Reliability of Digital Nanometric CMOS Circuits. In: 2011 Proceedings of nternational Symposium on Defect and Fault Tolerance in VLSI and Nanotechnology Systems, Vancouver, BC, (pp. 60–67). IEEE.

Verma, A. K., Brisk, P. & Ienne, P. (2008). Variable latency speculative addition: A new paradigm for arithmetic circuit design. In: 2008 Proceedings Design, Automation & Test in Europe Conference and Exhibition, (pp. 1250–1255). IEEE.

Kulkarni, P., Gupta, P., & Ercegovac, M. D. (2011). Trading accuracy for power in a multiplier architecture. Jounal of Low Power Electronics, 7(4), 490–501.

Shin D., & Gupta, S. K. (2010). Approximate logic synthesis for error tolerant applications. In: 2010 Proceedings Design, Automation & Test in Europe Conference and Exhibition, (pp. 957–960). IEEE.

Phillips, B. J., Kelly, D. R., & Ng, B. W. (2006). Estimating adders for a low density parity check decoder. Proc. SPIE, 6313, 631302.

Shin, D. & Gupta, S. K. (2008). A re-design technique for data path modules in error tolerant applications. In: Proceedings 17th Asian Test Symposium (pp. 431–437). IEEE.

Rabaey, J. M., Chandrakasan, A., & Nikolic, B. (2009). Digital integrated circuits a design perspective (2nd ed.). Delhi: PHI Learning.

Nagateja, T., Rao, T. V. & Srinivasulu, A. (2015). Low Voltage, High Speed FinFET Based 1-BIT BBL-PT Full Adders. In: 2015 Proceedings of International Conference on Communication and Signal Processing (ICCSP), Melmaruvathur, Tamilnadu, India, April 2–4, 2015, (pp. 1247–1251). IEEE. DOI: https://doi.org/10.1109/ICCSP.2015.7322707.

Sarada, M. & Srinivasulu, A. (2016). Fin-FET based 4-BIT input XOR/XNOR logic circuit. In: 2016 Proceedings of International Conference on Applied Electronics (AEIC-16), Sept 6-7, 2016, Pilsen, Czech Republic. (pp. 219-222) IEEE. DOI: https://doi.org/10.1109/AE.2016.7577277

Saini, J. K., Srinivasulu, A. & Singh, B. P. (2017). A new low-power full-adder cell for low voltage using CNTFETs. In: 2017 Proceedings of International Conference on Electronics, Computers and Artificial Intelligence (ECAI), Targoviste, Romania, 29 June-01 July, 2017, (pp. 6) IEEE. DOI: https://doi.org/10.1109/ECAI.2017.8166425.

Lakshmi, P. V., Sarada, M., Srinivasulu, A., & Pal, D. (2018). Three novel single-stage full swing 3-input XOR. International Journal of Electronics, 105(8), 1416–1432. https://doi.org/10.1080/00207217.2018.1460767.

Srinivasulu, A., Sravanthi, G., Sarada, M., & Pal, D. (2018). FinFET based Miller-Encoder for UHF and SHF RFID application. International Journal of Electronics, 105(1), 104–115. https://doi.org/10.1080/00207217.2017.1354401.

Sarada, M., Srinivasulu, A., & Pal, D. (2018). Novel low-supply, differential XOR/ XNOR with rail-to-rail swing, for hamming-code generation. International Journal of Electronics Letters, 6(3), 272–287. https://doi.org/10.1080/21681724.2017.1357761.

Author information

Authors and Affiliations

Corresponding author

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Tirupathireddy, A., Sarada, M. & Srinivasulu, A. Energy-efficient approximate adders for DSP applications. Analog Integr Circ Sig Process 107, 649–657 (2021). https://doi.org/10.1007/s10470-020-01768-w

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10470-020-01768-w