Abstract

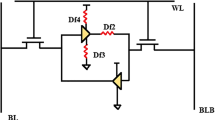

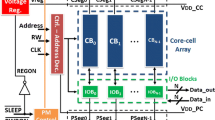

As technology advances, circuit density and complexity increases in integrated circuits which make the devices vulnerable to different types of manufacturing defects. In such cases, even the occurrence of a fault may be critical. Hence, ensuring Static random access memory (SRAM) reliability and quality with high priority is essential. In this paper, an innovative approach to SRAM testing—wavelet-based transient supply current testing with modified March sequence exploiting read equivalent stress (RES) is introduced for fault detection. The main contribution of this research work is the unique testing solution that ensures a minimum test time for the detection of open defects in SRAMs. In comparison with other techniques that solely rely on the hardware implementation for fault detection, the proposed technique reduces design parameters, such as the area overhead, power consumption, hardware complexity and performance overhead. The simulation results demonstrate that the proposed technique can provide high reliability and efficiency and reduce test time (25%) compared to other methods. A complete evaluation of the proposed technique in terms of the overall memory performance is presented in this work. The main objective of this study is to investigate the efficiency of wavelet-based transient current test in detecting all open defects targeted in this work in SRAMs amidst process variations. Moreover, the conventional test time of transient current test is minimized exploiting the effects of RES.

Similar content being viewed by others

References

Gomez, A. F., Lavratti, F., Medeiros, G., Sartori, M., Bolzani Poehis, L., Champac, V., et al. (2016). Effectiveness of a hardware-based approach to detect resistive open defects in SRAM cells under process variations. Microelectronics Reliability, 67, 150–158.

Ryan, P., Aziz, I. et al. (2014, October). Process defect trends and strategic test gaps. In 2014 IEEE international test conference (ITC) (pp. 1–8).

Nassif, S. R., Mehta, N., & Cao, Y. (2010, March). A resilience roadmap. In Design, automation test in Europe conference exhibition (DATE), 2010 (pp. 1011–1016).

Hamdioui, S., Al-Ars, Z., & van de Goor, A. J. (2002). VLSI “Testing static and dynamic faults in random access memories” 2002 (VTS 2002). In Proceedings 20th IEEE.

Marinescu. (1982). Simple and efficient algorithms for functional fault testing. In Proceedings of international test conference (pp. 236–239).

Hamdioui, S., van de Goor, A. J., & Rodgers, M. (2002). March SS—A test for all static simple SRAM faults. In Proceedings of the IEEE international workshop on memory technology, Journal of Design and Testing (MTDT 2002) (pp. 95–100).

Harutunyan, G., Vardanian, V. A., & Zorian, Y. (2005). Minimal march tests for unlinked static faults in random access memories. In Proceedings of 23rd VLSI test symposium (pp. 53–59).

Dilillo, L., Girard, P., Pravossoudovitch, S., Virazel, A., Borri, S., & Hage-Hassan, M. (2004). Resistive-open defects in embedded-SRAM core cells: analysis and march test solution. In 13th Asian test symposium.

Dilillo, L., Girard, P., Pravossoudovitch, S., Virazel, A., Borri, S., & Hage-Hassan, M. (2003). Data retention fault in SRAM memories: Analysis and detention procedures. In Proceedings of 23rd IEEE VLSI test symposium (VTS 05) (pp. 23–28).

Harutunyan, G., Vardanian, V. A., & Zorian, Y. (2007). Minimal March tests for detection of dynamic faults in random access memories. Journal of Electronic Testing, 23, 55–74.

Yoon, D. H., Kim, H. S., & Kang, S. (2001). Dynamic power supply current testing for open defects in CMOS SRAMs. ETRI Journal, 23(2), 77–84.

Kim, H.-S., Yoon, D.-H., & Kang, S. (2001). SRAM transparent testing methodology using dynamic power supply current. IEEE Proceedinsg of Circuit Devices and Systems, 148, 217–222.

Gyepes, G., Arbet, D., Brenkus, J., Stopjakova, V., & Mihalov, J. (2014). A new IDDT test approach and its efficiency in covering resistive opens in SRAM arrays. Microprocessors and Microsystems, 38(5), 359–367.

Bhunia, S., & Roy, K. (2002). Defect oriented testing of analog circuits using wavelet analysis of dynamic supply current. Journal of Electronic Testing-Theory and Applications, 21, 302–307.

Spinks, S. J., Chalk, C. D., Bell, I. M., & Zwolinski, M. (2004). Generation and verification of tests for analogue circuits subject to process parameter deviations. Journal of Electronic Testing, 20(1), 11–23.

Changgeng, Yu., Liu, G., & Lai, L. (2014). Diagnosis of resistive-open defects using IDDT in digital CMOS circuits. WSEAS Transactions on Circuits and Systems, 13, 296–300.

Sivamangai, N. M., & Gunavathi, K. (2011). Fault detection in SRAM cell using wavelet transform based transient current testing method. International Journal of Latest Trends in Software Engineering, 1(1), 20–27.

Princy P., Sivamangai, N. M., & Athira, S. (2017). An efficient fault detection technique in SRAM using wavelet transform. In International conference on innovations in electrical, electronics, instrumentation and media technology (ICEEIMT).

Princy P., & Sivamangai, N. M. (2019). An efficient wavelet based transient current test towards detection of data retention faults in SRAM. Journal of Electronic Testing Theory and Applications, 35, 473–483.

Niggemeyer, D., Redeker, M., & Otterstedet, J. (1998). Integration of non-classical faults in standard march tests. In Records of the IEEE international workshop on memory technology, design and testing (pp. 91–96).

Princy, Prince & Sivamangai, N. M. (2020). A novel technique for minimization of March test using read equivalent stress. International Journal of Nanomanufacturing, 16, 184–201.

Kinseher, J., Voelker, M., & Polian, I. (2017). Improving testability and reliability of advanced SRAM architectures. IEEE Transactions in Emerging Topics in Computing, 7, 456–467.

Author information

Authors and Affiliations

Corresponding author

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Prince, P., Sivamangai, N.M. A novel method for minimizing transient current test time by exploiting RES in SRAM. Analog Integr Circ Sig Process 107, 353–367 (2021). https://doi.org/10.1007/s10470-020-01747-1

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10470-020-01747-1