Abstract

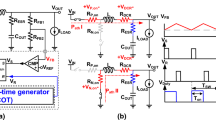

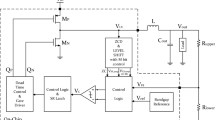

This paper proposes a three-level buck converter utilizing a Digital-to-Analog Converter (DAC)-based flying capacitor voltage control technique, which controls the voltage on a flying capacitor with a differential difference amplifier and common mode feedback circuit for stable operation. Employment of the DAC-based flying capacitor voltage control circuit allows the proposed circuit to compensate for the inductor voltage error as the load current varies. The proposed three-level buck converter was implemented with a CMOS 180 nm standard process. The measurement results demonstrate the wide range of the input and output voltage from 2.7 V to 3.6 V and 0.7 V to 2.4 V, respectively. The proposed three-level buck converter achieved the peak power efficiency of 91% and output ripple voltage of 32.5 mV at the switching frequency of 2 MHz and load current range of 10 mA to 400 mA.

Similar content being viewed by others

References

Wu, C., Takamiya, M., & Sakurai, T. (2018). Clocked hysteresis control scheme with power-law frequency scaling in buck converter to improve light-load efficiency for IoT sensor nodes. IEEE Transactions on Very Large Scale Integration (VLSI) Systems, 26(6), 1139–1150.

Cheng, C., Lau, R., Rathi, N., & Chung, H. (2019). Extraction of intrinsic parameters of lead-acid batteries using energy recycling technique. IEEE Transactions on Power Electronics, 34(5), 4765–4779.

Chen, X., Pise, A., Elmes, J., & Batarseh, I. (2019). Ultra-high efficient low-power bidirectional cascaded buck-boost converter for portable PV-battery-devices applications. IEEE Transactions on Industry Applications, 55(4), 3989–4000.

Kim, W., Brooks, D., & Wei, G. (2012). A fully-integrated 3-level DC–DC converter for nanosecond-scale DVFS. IEEE Journal of Solid-State Circuits, 47(1), 206–219.

Xue, J., & Lee, H. (2016). A 2 MHz 12–100 V 90% efficiency self balancing ZVS reconfigurable three-level DC-DC regulator with constant-frequency adaptive-on-time V2 control and nanosecond-scale ZVS turn-on delay. IEEE Journal of Solid-State Circuits, 51(12), 2854–2866.

Liu, X., Huang, C., & Mok, P. (2018). A high-frequency three-level buck converter with real-time calibration and wide output range for fast-DVS. IEEE Journal of Solid-State Circuits, 53(2), 582–595.

Chen, J., Hwang, Y., Chen, J.-H., Ku, Y., & Yu, C. (2018). A new fast-response current-mode buck converter with improved I2-controlled techniques. IEEE Transactions on Very Large Scale Integration (VLSI) Systems, 26(5), 903–911.

Tao, C., & Fayed, A. (2011). A buck converter with reduced output spurs using asynchronous frequency hopping. IEEE Transactions on Circuits and Systems II: Express Briefs, 58(11), 709–713.

Cheng, L., Liu, Y., & Ki, W. H. (2014). A 10/30 MHz fast reference-tracking buck converter with DDA-based type-III compernsator. IEEE Journal of Solid-State Circuits, 49(12), 2788–2799.

Chong, J., So, J., & Yoon, K. (2019). A CMOS PFM buck converter employing a digitally programmable voltage level-shifting technique. Analog Integrated Circuits and Signal Processing, 98(2), 321–329.

Acknowledgments

This research was supported in part by Inha University Research Grant and the National Research Foundation of Korea (NRF) grant funded by the Korea government (MSIT) National Research Foundation of Korea (2019R1F1A1050640). The chip was fabricated under the IDEC MPW program. The authors thank to anonymous reviewers.

Author information

Authors and Affiliations

Corresponding author

Additional information

Publisher’s Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

So, JW., Yang, HR., Park, SM. et al. Three-level buck converter utilizing a DAC-based flying capacitor voltage control technique. Analog Integr Circ Sig Process 107, 273–280 (2021). https://doi.org/10.1007/s10470-020-01738-2

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10470-020-01738-2