Abstract

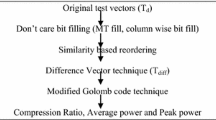

High temperature during test mode and the large volume of test data are the two prominent challenges in the testing of System-on-Chip (SoC). Temperature relies on the spatial power distribution between the blocks of the chip. An efficient don’t care filling technique is proposed to minimize the non-uniform spatial power distribution, which, in turn, reduces the peak temperature of the chip. However, high test data compression can be obtained by carefully mapping the don’t care bits to get more similar subvectors in the precomputed test patterns. The don’t care bits in the given test set can be utilized for test data compression and peak temperature reduction. As the same don’t care bits are to be used for both peak temperature reduction and test data compression, the two techniques conflict with each other. An integrated approach is presented to keep peak temperature under the safe limit with low test compression loss. Experimental results on ISCAS’89 benchmark circuits demonstrate the effectiveness of the proposed approach

Similar content being viewed by others

References

Hetherington G, Fryars T, Tamarapalli N, Kassab M, Hassan A, Rajski J (1999) Logic BIST for large industrial designs: real issues and case studies. In: Proc. of international Test Conference, pp 358–367

Murray BT, Hayes JP (1996) Testing ICs: getting to the core of the problem. Computer 29 (11):32–38

Wang L-T, Wu C-W, Wen X (2006) VLSI Test Principles and Architectures: Design for Testability , Elsevier

Sivanantham S, Mallick PS, Raja Paul Perinbam J (2014) Low-power selective pattern compression for scan-based test applications. Computers & Electrical Engineering 40(4):1053–1063

Basker P, Arulmurugan A (2012) Survey of low power testing of VLSI circuits. In: Proc. of International Conference on Computer Communication and Informatics, pp 1–7

Minsik Cho, Pan DZ (2006) PEAKASO: peak-temperature aware scan-vector optimization. In: 24th IEEE VLSI Test Symposium, pp 52–57

Yoneda T, Inoue M, Sato Y, Fujiwara H (2010) Thermal-uniformity-aware X-filling to reduce temperature-induced delay variation for accurate at-speed testing. In: Proc. of 28th VLSI Test Symposium (VTS), pp 188–193

Dutta A, Kundu S, Chattopadhyay S (2013) Thermal Aware Don’t Care Filling to Reduce Peak Temperature and Thermal Variance during Testing. In: Proc. of 22nd Asian Test Symposium. ISSN: 1081-7735, 2377-5386, pp 25–30

Touba NA (2006) Survey of Test Vector Compression Techniques. IEEE Design Test of Computers 23(4):294– 303

Lee K-J, Chen J-J, Huang C-H (1998) Using a single input to support multiple scan chains. In: Proc. of 1998 IEEE/ACM International Conference on Computer-Aided Design, pp 74–78

Li L, Chakrabarty K, Touba NA (2003) Test Data Compression Using Dictionaries with Selective Entries and Fixed-length Indices. ACM Trans. Des. Autom. Electron. Syst. 8(4):470– 490

Jas A, Ghosh-Dastidar J, Mom-Eng Ng, Touba NA (2003) An efficient test vector compression scheme using selective Huffman coding. IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems 22(6):797–806

Wolff FG, Papachristou C (2002) Multiscan-based test compression and hardware decompression using LZ77. In: Proc. of International Test Conference, pp 331–339

Chandra A, Chakrabarty K (2001) System-on-a-chip test-data compression and decompression architectures based on Golomb codes. IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems 20(3):355–368

Chandra A, Chakrabarty K (2003) Test data compression and test resource partitioning for system-on-a-chip using frequency-directed run-length (FDR) codes. IEEE Trans Comput 52(8):1076–1088

El-Maleh AH, Al-Abaji RH (2002) Extended frequency-directed run-length code with improved application to system-on-a-chip test data compression. In: Proc. of 9th International Conference on Electronics, Circuits and Systems, vol 2, pp 449–452

Tehranipoor M, Nourani M, Chakrabarty K (2005) Nine-coded compression technique for testing embedded cores in SoCs. IEEE Transactions on Very Large Scale Integration (VLSI) Systems 13(6):719–731

Almukhaizim S, Alsubaihi S, Sinanoglu O (2010) On the application of dynamic scan chain partitioning for reducing peak shift power. J Electron Test 26(4):465–481

Arvaniti E, Tsiatouhas Y (2014) Low-power scan testing: a scan chain partitioning and scan hold based technique. J Electron Test 30(3):329–341

Kumar SK, Kundu S, Chattopadhyay S (2012) Customizing completely specified pattern set targeting dynamic and leakage power reduction during testing. Integration 45(2):211–221

Chandra A, Chakrabarty K (2002) Low-power scan testing and test data compression for system-on-a-chip. IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems 21(5):597–604

Chandra A, Chakrabarty K (2003) A unified approach to reduce SOC test data volume, scan power and testing time. IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems 22(3):352–363

Li J, Liu X, Zhang Y, Hu Y, Li X, Xu Q (2011) Capture-power-aware test data compression using selective encoding. Integration 44(3):205–216

Karmakar R, Chattopadhyay S (2015) Thermal-Aware Test Data Compression Using Dictionary Based Coding. In: Proc. 28th International Conference on VLSI Design, pp 53–58

Karmakar R, Chattopadhyay S (2017) Temperature and data size trade-off in dictionary based test data compression. Integration 57:20–33

Azhaganantham A, Govindasamy M (2018) Genetic algorithm-based thermal uniformity–aware x-filling to reduce peak temperature during testing. Measurement and Control 51(7-8):235–242

Chattopadhyay S, Choudhary N (2003) Genetic algorithm based approach for low power combinational circuit testing. In: Proc. of 16th International Conference on VLSI Design, pp 552– 557

Seong S, Mishra P (2008) Bitmask-Based Code Compression for Embedded Systems. IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems 27(4):673–685

Hamzaoglu I, Patel JH (2000) Test set compaction algorithms for combinational circuits. IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems 19(8):957–963

Stan MR, Skadron K, Barcella M, Huang W, Sankaranarayanan K, Velusamy S (2003) HotSpot: a dynamic compact thermal model at the processor-architecture level. Microelectron J 34(12):1153–1165

Author information

Authors and Affiliations

Corresponding author

Additional information

Responsible Editor: C. A. Papachristou

Publisher’s Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Arulmurugan, A., Murugesan, G. & Vivek, B. Thermal-aware Test Data Compression for System-on-Chip Based on Modified Bitmask Based Methods. J Electron Test 36, 577–590 (2020). https://doi.org/10.1007/s10836-020-05902-4

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10836-020-05902-4