Abstract

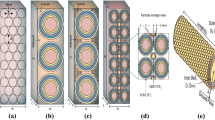

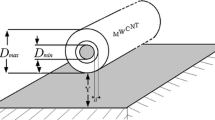

The continuous miniaturization of very large-scale integration devices impacts the performance of integrated circuits. The performance of existing interconnect materials such as copper has become saturated beyond the deep-submicron technology node, motivating the search for new interconnect materials that could be efficiently employed in such circuits. In this study, a temperature-dependent analysis is performed to determine the propagation delay, power dissipation, and power–delay product of copper, single-walled carbon nanotubes (SWCNTs), multiwalled carbon nanotubes (MWCNTs), double-walled carbon nanotubes (DWCNTs), and mixed (multi- and double-wall) carbon nanotube bundle (MDCB) structures. The performance of these bundled structures is examined with the help of a complementary metal–oxide–semiconductor driver interconnect load system at various temperatures (200–500 K) and technology nodes (22 and 16 nm). The proposed novel mixed structure with MWCNTs at the periphery and DWCNTs in the center is interesting due to the combination of the excellent conducting properties of DWCNTs and the reduction of the net capacitive coupling due to the MWCNTs. Indeed, it is observed that this MDCB interconnect structure can outperform not only copper interconnects but also the SWCNT, MWCNT, and DWCNT structures. Such mixed structures could be used as interconnect materials in high-speed integrated circuits at future nanotechnology nodes.

Similar content being viewed by others

References

Wei, B.Q., Vajtai, R., Ajayan, P.M.: Reliability and current carrying capacity of carbon nanotubes. Appl. Phys. Lett. 79(8), 1172–1174 (2001)

Kreupl, F., Graham, A.P., Duesberg, G.S., Steinhogl, W., Liebau, M., Unger, E., Honlein, W.: Carbon nanotubes in interconnect applications. Microelectron. Eng. 64(1), 399–408 (2002)

McEuen, P.L., Fuhrer, M.S., Park, H.: Single-walled carbon nanotube electronics. IEEE Trans. Nanotechnol. 99(1), 78–85 (2002)

Naeemi, A., Sarvar, R., Meindl, J.D.: Performance comparison between carbon nanotube and copper interconnects for gigascale integration (GSI). IEEE Electron Device Lett. 26(2), 84–86 (2005)

Li, H., Banerjee, K.: High-frequency analysis of carbon nanotube interconnects and implications for on-chip inductor design. IEEE Trans. Electron Devices 56(10), 2202–2214 (2009)

Litoria, P., Sandha, K.S., Kansal, A.: Impact of tunneling conductance on the performance of multi-walled carbon nanotubes as VLSI interconnects for nano-scaled technology nodes. J. Mater. Sci. Mater. Electron. 28(6), 4818–4827 (2017)

Raychowdhury, A., Roy, K.: Modeling of metallic carbon-nanotube interconnects for circuit simulations and a comparison with Cu interconnects for scaled technologies. IEEE Trans. Comput. Aided Des. Integr. Circuits Syst. 25(1), 58–65 (2005)

Steinhogl, W., Schindler, G., Steinlesberger, G., Traving, M., Engelhardt, M.: Comprehensive study of the resistivity of copper wires with lateral dimensions of 100 nm and smaller. J. Appl. Phys. 97(2), 023706(1–7) (2005)

Venkataraman, A., Amadi, E.V., Chen, Y., Papadopoulos, C.: Carbon nanotube assembly and integration for applications. Nanoscale Res. Lett. 14(1), 1–47 (2019)

Hsu, W.J., Miao, H.Y., Liu, J.H.: A study on the electric property of buckypaper by eddy current testing. In: IEEE Nanotechnology Materials and Devices Conference, pp. 137–140, Jeju, South Korea (2011)

Rai, M.K., Sarkar, S.: Influence of tube diameter on carbon nanotube interconnect delay and power output. Phys. Status Solidi (A) 208(3), 735–739 (2011)

Rai, M.K., Sarkar, S.: Influence of distance between adjacent tubes on SWCNT bundle interconnect delay and power dissipation. J. Comput. Electron. 12(4), 796–802 (2013)

Das, D., Rahaman, H.: Analysis of crosstalk in single- and multiwall carbon nanotube interconnects and its impact on gate oxide reliability. IEEE Trans. Nanotechnol. 10(6), 1362–1370 (2011)

Srivastava, N., Banerjee, K.: Performance analysis of carbon nanotube interconnects for VLSI applications. In: ICCAD Proceedings, IEEE/ACM International Conference on Computer-Aided Design, pp. 383–390, San Jose, CA, USA (2005)

Haruehanroengra, S., Wang, W.: Analyzing conductance of mixed carbon-nanotube bundles for interconnect applications. IEEE Electron Device Lett. 28(8), 756–759 (2007)

Zhu, L., Sun, Y., Hess, D.W., Wong, C.P.: Well-aligned open-ended carbon nanotube architectures: an approach for device assembly. Nano Lett. 6(2), 243–247 (2006)

Sathyakam, P.U., Mallick, P.S.: Transient analysis of mixed carbon nanotube bundle interconnects. Electron. Lett. 47, 1134–1135 (2011)

Sathyakam, P.U., Mallick, P.S.: Inter-CNT capacitance in mixed CNT bundle interconnects for VLSI circuits. Int. J. Electron. 99(10), 1439–1447 (2012)

Subash, S., Kolar, J., Chowdhury, M.H.: A new spatially rearranged bundle of mixed carbon nanotubes as VLSI interconnection. IEEE Trans. Nanotechnol. 12(1), 3–12 (2013)

Majumder, M.K., Kumar, J., Kaushik, B.K.: Process-induced delay variation in SWCNT, MWCNT, and mixed CNT interconnects. IETE J. Res. 61(5), 533–540 (2015)

Parihar, T., Sharma, A.: A comparative study of Mixed CNT bundle with Copper for VLSI Interconnect at 32 nm. Int. J. Eng. Trends Technol. (IJETT) 4(4), 1145–1150 (2013)

Rai, M.K., Garg, H., Kaushik, B.K.: Temperature-dependent modeling and crosstalk analysis in mixed carbon nanotube bundle interconnects. J. Electron. Mater. 46(8), 5324–5337 (2017)

Majumder, M.K., Pandya, N.D., Kaushik, B.K., Manhas, S.K.: Dynamic crosstalk effect in mixed CNT bundle interconnects. Electron. Lett. 48(7), 384–385 (2012)

Kumar, A., Vobulapuram, R.K., Kaushik, B.K.: Transient analysis of crosstalk induced effects in mixed CNT bundle interconnects using FDTD technique. IEEE Trans. Electromagn. Compat. 61, 1621–1629 (2018)

Sun, S., Mu, W., Edwards, M., Mencarelli, D., Pierantoni, L., Fu, Y., Jeppson, K., Liu, J.: Vertically aligned CNT-Cu nano-composite material for stacked through-silicon-via interconnects. Nanotechnology 27(33), 335705 (2016)

Subash, S., Chowdhury, M.H.: Mixed carbon nanotube bundles for interconnect applications. Int. J. Electron. 96(6), 657–671 (2009)

Sandha, K.S., Raj, B.: Performance and analysis of temperature dependent multi-walled carbon nanotubes as global interconnects at different technology nodes. J. Comput. Electron. 14(2), 469–476 (2015)

Sandha, K.S., Raj, B.: Temperature-dependent modeling and performance evaluation of multi- walled CNT and single-walled CNT as global interconnects. J. Electron. Mater. 44(12), 4825–4835 (2015)

Sandha, K.S., Raj, B.: Influence of temperature on MWCNT bundle, SWCNT bundle and Copper interconnects for nanoscaled technology nodes. J. Mater. Sci. Mater. Electron. 26(8), 6134–6142 (2015)

Pop, E., Sinha, S., Goodson, K.E.: Heat generation and transport in nanometer-scale transistors. Proc. IEEE 94(8), 1587–1601 (2006). https://doi.org/10.1109/JPROC.2006.879794

Pop, E., Mann, D.A., Goodson, K.E., Dai, H.: Electrical and thermal transport in metallic single-wall carbon nanotubes on insulating substrates. J. Appl. Phys. 101(9), 93710 (2007)

Mohsin, K.M., Srivastava, A., Sharma, A.K., Mayberry, C., Fahad, M.S.: Temperature sensitivity of electrical resistivity of graphene/copper hybrid nano ribbon interconnect: a first principle study. ECS J. Solid State Sci. Technol. 6(4), 119–124 (2017)

Hosseini, A., Shabro, V.: Thermally-aware modeling and performance evaluation for single-walled carbon nanotube-based interconnects for future high performance integrated circuits. Microelectron. Eng. 87(1), 1955–1962 (2010)

Rai, M.K., Sarkar, S.: Temperature dependent crosstalk analysis in coupled single-walled carbon nanotube (SWCNT) bundle interconnects. Int. J. Circ. Theor. App. 43(10), 1367–1378 (2015)

Rai, M.K., Kaushik, B.K., Sarkar, S.: Thermally aware performance analysis of single-walled carbon nanotube bundle as VLSI interconnects. J. Comput. Electron. 15(2), 407–419 (2016)

Burke, P.J.: Luttinger liquid theory as a model of the gigahertz electrical properties of carbon nanotubes. IEEE Trans. Nanotechnol. 99(3), 129–144 (2002)

Li, H., Yin, W.Y., Banerjee, K., Mao, J.F.: Circuit modeling and performance analysis of multi-walled carbon nanotube interconnects. IEEE Trans. Electron Devices 55(6), 1328–1337 (2008)

Pu, S.N., Yin, W.Y., Mao, J.F., Liu, Q.H.: Crosstalk prediction of single- and double-walled carbon-nanotube (SWCNT/DWCNT) bundle interconnects. IEEE Trans. Electron Devices 56(4), 560–568 (2009)

Im, S., Srivastava, N., Banerjee, K., Goodson, K.E.: Scaling analysis of multilevel interconnect temperatures for high-performance ICs. IEEE Trans. Electron Devices 52(12), 2710–2719 (2005)

Predictive Technology Model (PTM). http://www.eas.asu.edu/ptm/. Accessed 21 June 2019

Semiconductor Industry Association, International Technology Roadmap for Semiconductors (ITRS). http://www.itrs.net/. Accessed 26 June 2019

Author information

Authors and Affiliations

Corresponding author

Ethics declarations

Conflict of interest

The authors declare that they have no conflicts of interest.

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Dhillon, G., Sandha, K.S. Mixed CNT bundles as VLSI interconnects for nanoscale technology nodes. J Comput Electron 20, 248–258 (2021). https://doi.org/10.1007/s10825-020-01585-4

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10825-020-01585-4