Abstract

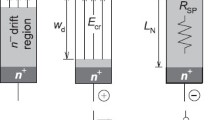

High-voltage fast recovery diodes (FRDs) are characterized by a small forward voltage drop and low power dissipation. The main characteristics of such diodes is the reverse blocking voltage or the breakdown voltage. The aim of this work is to develop a guard ring topology allowing us to obtain the maximum possible blocking voltage of the diode and definite localization of the breakdown place under the conditions of the standard technological processes and without using new materials or substrates. The topology of the high-voltage part of silicon fast recovery power diodes is developed to obtain the maximum reverse blocking voltage. The calculations are carried out in the TCAD environment in the structure editor of which we included a program for the automatic creation of device models with dimensions of about several millimeters. The arrangement of guard rings is calculated according to the proposed principle allowing us to obtain power diodes with different breakdown voltages. The topology is developed so that the breakdown occurs under the edge of the active region, which guarantees the absence of catastrophic failures of the device. Power fast recovery diodes manufactured according to the proposed topology have the maximum reverse blocking voltage within the range of 3.3–6.7 kV, which indicates the reliability of the calculation methodology.

Similar content being viewed by others

REFERENCES

Vellvehi, M., Flores, D., Jorda, X., et al., Design and optimization of suitable edge terminations for 6.5 kV IGBTs, Microelectron. J., 2002, vol. 33, pp. 765–769.

Ciappa, M., Some reliability aspects of IGBT modules for high-power applications, Doctoral Thesis, Zurich: Swiss Fed. Inst. Technol., 2001.

Humbel, O., Application-specific improvements on fast recovery 4.5 kV press-pack rectifiers, Doctoral Thesis, Zurich: Swiss Fed. Inst. Technol., 2000.

Baliga, J.B., Fundamentals of Power Semiconductor Devices, New York: Springer Science, 2008, pp. 1–163.

Kopta, A., High voltage silicon based devices for energy efficient power distribution and consumption, in Proceedings of the Electron Devices Meeting IEDM, IEEE Int., 2014, pp. 2.4.1–2.4.4.

Baliarda, A.V., Avalanche ruggedness of local charge balance power super junction transistors, Doctoral Thesis, Barcelona: Auton. Univ. Barcelona, 2013.

Netzel, M. and Herzer, R., Simulation of complex planar edge termination structures for vertical igbts by solving the complete semiconductor device equations, Simul. Semicond. Dev. Process., 1995, vol. 6, pp. 290–293.

Baradai, N., Sanfilippo, C., Carta, R., et al., An improved methodology for the CAD optimization of multiple floating field-limiting ring terminations, IEEE Trans. Electron Dev., 2001, vol. 58, no. 1, pp. 266–270.

Vecchi, M.C. and Rudan, M., Modeling electron and hole transport with full-band structure effects by means of the spherical-harmonics expansion of the BTE, IEEE Trans. Electron Dev., 1998, vol. 45, no. 1, pp. 230–238.

Author information

Authors and Affiliations

Corresponding author

Additional information

Translated by A. Nikol’skii

Rights and permissions

About this article

Cite this article

Sopova, O., Kritskaya, T. Developing the Guard Ring Topology of Power Silicon Diodes with a Blocking Voltage of up to 6.7 kV. Russ Microelectron 48, 462–466 (2019). https://doi.org/10.1134/S1063739719070151

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1134/S1063739719070151