Abstract

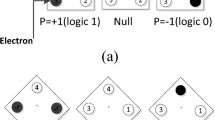

Quantum-dot cellular automata (QCA) is known as one of the best alternative technologies for CMOS on nano-scale dimensions, which allows the design of digital circuits with high speed and density. Decoders are considered as one of the most widely used combinational circuits. They also play an important role in designing circuits such as FPGA, CLB, and memory addressing. In this paper, we propose an effective design of the 2-to-4 decoder in the QCA technology. The proposed design consists of only three inverter gates and six 3-input majority gates. Two single-layer and three-layer of the proposed 2-to-4 QCA decoder with only 56 and 62 cells are provided and they require 3 and 4 clock cycles respectively. Also, one multi-layer 3-to-8 QCA decoder is developed and implemented using the proposed 2-to-4 QCA decoder. The proposed circuits are simulated using the QCADesigner 2.0.3 tool. A comparison of the proposed 2-to-4 QCA decoder with related designs shows that the proposed decoder has a good performance in terms of the number of cells, the occupied area, and the delay criteria. Also, the QCAPro tool is used to compute the power dissipation of the proposed decoder. Finally, the results are affirmed by physical proofs.

Similar content being viewed by others

References

Abedi D, Jaberipur G, Sangsefidi M (2015) Coplanar full adder in quantum-dot cellular automata via clock-zone-based crossover. IEEE Trans Nanotechnol 14(3):497–504

Ahmadpour S-S, Mosleh M (2018) A novel fault-tolerant multiplexer in quantum-dot cellular automata technology. J Supercomput 74(9):4696–4716

Ahmadpour, SS, Mosleh M (2019a) A novel ultradense and low‐power structure for fault‐tolerant three‐input majority gate in QCA technology. Concurr Comput Pract Exp 32:e5548

Ahmadpour S-S, Mosleh M (2019b) New designs of fault-tolerant adders in quantum-dot cellular automata. Nano Commun Netw 19:10–25

Ahmadpour S-S, Mosleh M, Heikalabad SR (2018) A revolution in nanostructure designs by proposing a novel QCA full-adder based on optimized 3-input XOR. Physica B 550:383–392

Ahmadpour SS, Mosleh M, Rasouli Heikalabad S (2019) Robust QCA full-adders using an efficient fault-tolerant five-input majority gate. Int J Circuit Theory Appl 47:1037–1056

Ahmadpour S-S, Mosleh M, Heikalabad SR (2020) An efficient fault-tolerant arithmetic logic unit using a novel fault-tolerant 5-input majority gate in quantum-dot cellular automata. Comput Electr Eng 82:106548

Asfestani MN, Heikalabad SR (2017) A unique structure for the multiplexer in quantum-dot cellular automata to create a revolution in design of nanostructures. Physica B 512:91–99

Bahar AN, Wahid KA (2019) Design of QCA-serial parallel multiplier (QSPM) with energy dissipation analysis. In: IEEE transactions on circuits and systems II: express briefs

Campos CAT et al (2015) USE: a universal, scalable, and efficient clocking scheme for QCA. IEEE Trans Comput Aided Des Integr Circuits Syst 35(3):513–517

De D, Purkayastha T, Chattopadhyay T (2016) Design of QCA based programmable logic array using decoder. Microelectron J 55:92–107

Fam SR, Navimipour NJ (2019) Design of a loop-based random access memory based on the nanoscale quantum dot cellular automata. Photon Netw Commun 37(1):120–130

Faraji H, Mosleh M (2018) A fast wallace-based parallel multiplier in quantum-dot cellular automata. Int J Nano Dimens 9(1):68–78

Feynman RP (1986) Quantum mechanical computers. Found Phys 16(6):507–531

Gadim MR, Navimipour NJ (2018) A new three-level fault tolerance arithmetic and logic unit based on quantum dot cellular automata. Microsyst Technol 24:1–11

Gargini P (2000) The international technology roadmap for semiconductors (ITRS):” past, present and future”. In: GaAs IC symposium, 2000. 22nd Annual, IEEE

Halloun IA, Hestenes D (1985) Common sense concepts about motion. Am J Phys 53(11):1056–1065

Kianpour M, Sabbaghi-Nadooshan R (2011) A novel modular decoder implementation in quantum-dot cellular automata (QCA). In: 2011 international conference on nanoscience, technology and societal implications (NSTSI), IEEE

Kianpour M, Sabbaghi-Nadooshan R (2014) A conventional design and simulation for CLB implementation of an FPGA quantum-dot cellular automata. Microprocess Microsyst 38(8):1046–1062

Kianpour, M, Sabbaghi-Nadooshan R (2015) A novel quantum-dot cellular automata ${X} $-bit $\times 32$-bit SRAM. IEEE Trans Very Large Scale Integr VLSI Syst 24(3):827–836

McDermott LC (1984) Research on conceptual understanding in mechanics. Phys Today 37:24–32

Nejad MY, Mosleh M (2017) A review on QCA multiplexer designs. Majlesi J Electri Eng 11(2):69

Noorallahzadeh M, Mosleh M (2019a) Parity-preserving reversible flip-flops with low quantum cost in nanoscale. J Supercomput 76:1–33

Noorallahzadeh M, Mosleh M (2019b) Efficient designs of reversible latches with low quantum cost. IET Circuits Dev Syst 13:806–815

Pourtajabadi R, Nayeri M (2019) A novel design of a multi-layer 2: 4 decoder using quantum-dot cellular automata. J Optoelectron Nanostruct 4(1):39–50

Sabbaghi-Nadooshan R (2014) A novel quantum-dot cellular automata CLB of FPGA. J Comput Electron 13(3):709–725

Sabbaghi-Nadooshan R, Kianpour M (2014) A novel QCA implementation of MUX-based universal shift register. J Comput Electron 13(1):198–210

Sandhu A, Gupta S (2019) Performance evaluation of an efficient five-input majority gate design in QCA nanotechnology. Iran J Sci Technol Trans Electri Eng, 1–12

Seyedi S, Navimipour NJ (2017) An optimized design of full adder based on Nanoscale quantum-dot cellular automata. Opt-Int J Light Electron Opt 158:2243–2256

Seyedi S, Navimipour NJ (2018a) Design and evaluation of a new structure for fault-tolerance full-adder based on quantum-dot cellular automata. Nano Commun Netw 16:1–9

Seyedi S, Navimipour NJ (2018b) An optimized three-level design of decoder based on nanoscale quantum-dot cellular automata. Int J Theor Phys 57(7):2022–2033

Seyedi S, Ghanbari A, Navimipour NJ (2019a) New design of a 4-bit ripple carry adder on a nano-scale quantum-dot cellular automata. Mosc Univ Phys Bull 74(5):494–501

Seyedi S, Darbandi M, Navimipour NJ (2019b) Designing an efficient fault tolerance D-latch based on quantum-dot cellular automata nanotechnology. Optik 185:827–837

Sherizadeh R, Navimipour NJ (2018) Designing a 2-to-4 decoder on nanoscale based on quantum-dot cellular automata for energy dissipation improving. Opt-Int J Light Electron Opt 158:477–489

Srivastava S, et al (2011) QCAPro-an error-power estimation tool for QCA circuit design. In: International symposium on circuits and systems (ISCAS), 2011 IEEE, IEEE

Vankamamidi V, Ottavi M, Lombardi F (2008) Two-dimensional schemes for clocking/timing of QCA circuits. IEEE Trans Comput Aided Des Integr Circuits Syst 27(1):34–44

Vetteth A, et al (2002) Quantum-dot cellular automata carry-look-ahead adder and barrel shifter. In: IEEE emerging telecommunications technologies conference

Walus K et al (2004) QCADesigner: a rapid design and simulation tool for quantum-dot cellular automata. IEEE Trans Nanotechnol 3(1):26–31

Wang W, Walus K, Jullien GA (2003) Quantum-dot cellular automata adders In: Third ieee conference on nanotechnology, 2003. IEEE-NANO 2003. IEEE

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Ahmadpour, SS., Mosleh, M. & Asadi, MA. The Development of an Efficient 2-to-4 Decoder in Quantum-Dot Cellular Automata. Iran J Sci Technol Trans Electr Eng 45, 391–405 (2021). https://doi.org/10.1007/s40998-020-00375-9

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s40998-020-00375-9