Abstract

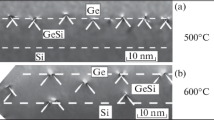

It has been shown that threading dislocations may be removed from patterned mismatched heteroepitaxial layers through a process of dislocation sidewall gettering (DSG), also known as patterned heteroepitaxial processing (PHeP). This gettering approach involves the glide of dislocations toward sidewalls, where they become trapped by image forces. Simple quantitative models have been developed for DSG, but they fail to explain why only partial removal of dislocations was observed in ZnSSe/GaAs (001) whereas complete removal has been achieved in ZnSe/GaAs (001) with higher lattice mismatch. Until now this phenomenon has been qualitatively explained by the presence of sessile dislocations. Here we present a quantitative model for pinning interactions and show that these interactions can limit the growth of misfit dislocation segments and thereby reduce the effectiveness of DSG in ZnSySe1-y/GaAs (001) relative to ZnSe/GaAs (001).

Similar content being viewed by others

References

X.G. Zhang, P. Li, G. Zhao, D.W. Parent, F.C. Jain, and J.E. Ayers, J. Electron. Mat. 27, 1248 (1998).

X. G. Zhang, A. Rodriguez, X. Wang, P. Li, F. C. Jain, and J. E. Ayers, in 2000 U. S. Workshop on the Physics and Chemistry of II-VI Materials, Albuquerque, NM, USA (2000)

X.G. Zhang, A. Rodriguez, X. Wang, P. Li, F.C. Jain, and J.E. Ayers, Appl. Phys. Lett. 77, 2524 (2000).

X. G. Zhang, A. Rodriguez, P. Li, F. C. Jain, and J. E. Ayers, Materials Research Society Fall Meeting, Boston, MA (2000).

X. G. Zhang, A. Rodriguez, P. Li, F. C. Jain, and J. E. Ayers, in Connecticut Microelectronics and Optoelectronics Symposium, Storrs, CT (2001).

X.G. Zhang, A. Rodriguez, P. Li, F.C. Jain, and J.E. Ayers, J. Electron. Mater. 30, 667 (2001).

X.G. Zhang, A. Rodriguez, P. Li, F.C. Jain, and J.E. Ayers, J. Appl. Phys. 91, 3912 (2002).

J.E. Ayers, T. Kujofsa, P. Rago, and J.E. Raphael, Heteroepitaxy of Semiconductors: Theory, Growth, and Characterization, 2nd ed. (Boca Raton, FL: CRC Press, 2017).

T. Kujofsa and J. E. Ayers, in Materials Science and Technology Conference, Portland, OR (2019).

J.W. Matthews and A.E. Blakeslee, J. Cryst. Growth 27, 118 (1974).

J.W. Matthews, S. Mader, and T.B. Light, J. Appl. Phys. 41, 3800 (1970).

B.W. Dodson and J.Y. Tsao, Erratum: Relaxation of Strained‐Layer Semiconductor Structures via Plastic Flow [Appl. Phys. Lett., 51, 1325 (1987)]. Appl. Phys. Lett. 52, 825 (1988).

T. Kujofsa, W. Yu, S. Cheruku, B. Outlaw, S. Xhurxhi, F. Obst, D. Sidoti, B. Bertoli, P.B. Rago, E.N. Suarez, F.C. Jain, and J.E. Ayers, J. Electron. Mater. 41, 2993 (2012).

B. Bertoli, E.N. Suarez, J.E. Ayers, and F.C. Jain, J. Appl. Phys. 106, 073519 (2009).

T. Kujofsa and J.E. Ayers, Semicond. Sci. Technol. 31, 115014 (2016).

T. Kujofsa, Y. Song, and J.E. Ayers, Mater. Res. Express 5, 025909 (2018).

M. Cai, T. Kujofsa, X. Chen, M.T. Islam, and J.E. Ayers, Int. J. High Speed Electron. Syst. 27, 1840022 (2018).

Acknowledgments

This work has been made possible by financial support from Epitax Engineering.

Author information

Authors and Affiliations

Corresponding author

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Kujofsa, T., Ayers, J.E. Dislocation Sidewall Gettering in II-VI Semiconductors and the Effect of Dislocation Pinning Interactions. J. Electron. Mater. 49, 6977–6982 (2020). https://doi.org/10.1007/s11664-020-08353-x

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s11664-020-08353-x