Abstract

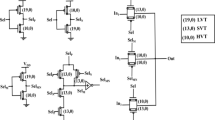

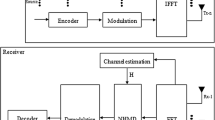

A micro-programmed Reconfigurable Parallel Finite Impulse Response (RPFIR) filter which can be used as subsystem in wireless sensor node is described in this work. High throughput is achieved using parallel processing and the power consumption is reduced using Vertical Horizontal Binary Common Sub expression Elimination (VHBCSE)-Reconfigurable Multiple Constant Multiplication (RMCM) based multiplier. The logical depth and logical elements are reduced using VHBCSE method. In the existing method, four 8*8 multipliers are used as two operand multiplier in the design of micro-programmed FIR. The two operand multiplier consumes more area and power when compared with Constant Multipliers (CM). The CM has been designed by using only adder, shifters and multiplexers, which consume less area and less power comparing with convention multipliers. The VHBCSE technique is used to find the redundant terms present within and adjutant coefficients, which in turn reduces the number of shifter, adder and multiplexer in the RMCM multiplier. This paper proposes the design of RPFIR filter based on VHBCSE technique which increases the throughput and reduces area and power consumption. It has been found that the power consumption of designed filter is reduced by 28% and throughput is increased by 4 times when compared with the existing FIR filters. Parallel processing used in this proposed system increases the throughput and VHBCSE technique reduces the redundant hardware and power dissipation. Experimental results are obtained for the proposed filter in FPGA platform and ASIC 180 nm technology. Finally, the results are compared with the existing works. The proposed parallel FIR filter will be suitable for implementation of a sensor node in ASIC and FPGA.

Similar content being viewed by others

References

Li, W., Wang, Z., Wei, G., Ma, L., Hu, J., Ding, D. (2015). A survey on multisensor fusion and consensus filtering for sensor networks. Discrete Dynamics in Nature and Society, 2015, 1–12. https://www.hindawi.com/journals/ddns/2015/683701/

Schizas, I. D., Ribeiro, A., & Giannakis, G. B. (2008). Consensus in ad hoc WSNs with noisy links—Part I: Distributed estimation of deterministic signals. IEEE Transactions on Signal Processing, 56(1), 350–364.

Abdelgawad, A., Abdelhak, S., Ghosh, S., & Bayoumi, M. (2009). A low-power multiplication algorithm for signal processing in wireless sensor networks. In IEEE (pp. 695–698).

BenSaleh, M. S., Qasim, S. M., Al Juffri, A. A., & Obeid, A. M. (2014). Scalable design of microprogrammed digital FIR filter for sensor processing subsystem. IEICE Electronic Express, 11(14), 1–7.

Lim, Y. C., Evans, J. B., & Liu, B. (1991). Decomposition of binary integers into signed power-of-two terms. IEEE Transactions on Circuits and Systems, 38(6), 667–672.

Hertley, R. I. (1996). Subexpression sharing in filters using canonic signed digit multipliers. IEEE Transactions on Circuits and Systems II, Analog and Digital Signal Processing, 43(10), 677–688.

Park, I. C., & Kang, H. J. (2002). Digital filter synthesis based on an algorithm to generate all minimal signed digit representations. IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, 21(12), 1525–1529.

Vun, C. H., Premkumar, A. B., & Zhang, W. (2013). A new RNS based DA approach for inner product computation. IEEE Transactions on Circuits Systems I, Regular Papers, 60(8), 2139–2152.

Kouretas, I., Basetas, C., & Paliouras, V. (2013). Low-power logarithmic number system addition/subtraction and their impact on digital filters. IEEE Transactions on Computers, 62(11), 2196–2209.

Gustafsson, O. (2007, May). A difference based adder graph heuristic for multiple constant multiplication problems. In IEEE international symposium on circuits and systems (ISCAS’07) (pp. 1097–1100).

Pan, Y., & Meher, P. K. (2014). Bit-level optimization of adder-trees for multiple constant multiplications for efficient FIR filter implementation. Transactions on Circuits and Systems I: Regular Papers, 61(2), 455–462.

Vinod, A. P., Lai, E., Maskell, D. L., & Meher, P. K. (2010). An improved common subexpression elimination method for reducing logic operators in FIR filter implementations without increasing logic depth. Integration the VLSI Journal, 43(1), 124–135.

Vinod, A. P., & Lai, E. M. K. (2005). An efficient coefficient partitioning algorithm for realizing low-complexity digital filters. IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, 24(12), 1936–1946.

Mahesh, R., & Vinod, A. P. (2010). Newreconfigurable architectures for implementing FIR filters with low complexity. IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, 29(2), 275–288.

Hatai, I., Chakrabarti, I., & Banerjee, S. (2015). An Efficient constant multiplier architecture based on vertical horizontal binary common sub-expression elimination algorithm for reconfigurable FIR filter synthesis. IEEE Transactions on Circuits and Systems I: Regular, 62(4), 1071–1080.

Parker, D. A., & Parhi, K. K. (1997). Low-area/power parallel FIR digital filter implementations. Journal of VLSI Signal Processing-Systems, 17(1), 75–92.

Chung, J. G., & Parhi, K. K. (2002). Frequency-spectrum-based low-area low-power parallel FIR filter design EURASIP. Journal on Applied Signal Processing, 2002(9), 444–453.

Parhi, K. K. (1999). VLSI digital signal processing systems: Design and implementation. New York: Wiley.

Mou, Z.-J., & Duhamel, P. (1991). Short-length FIR filters and their use in fast nonrecursive filtering. IEEE Transactions on Signal Processing, 39(6), 1322–1332.

Acha, J. I. (1989). Computational structures for fast implementation of L-path and L-block digital filters. IEEE Transactions on Circuits and Systems, 36(6), 805–812.

Cheng, C., & Parhi, K. K. (2004). Hardware efficient fast parallel FIR filter structures based on iterated short convolution. IEEE Transactions on Circuits and Systems—Part I: Regular Papers, 51(8), 1492–1500.

Cheng, C., & Parhi, K. K. (2005) Furthur complexity reduction of parallel FIR filters. In Proceedings of the IEEE international symposium on circuits and systems (ISCAS 2005) (May 2005), Kobe, Japan.

Cheng, C., & Parhi, K. K. (2007). Low-cost parallel FIR structures with 2-stage parallelism. IEEE Transactions on Circuits and Systems—Part I: Regular Papers, 54(2), 280–290.

Tsao, Y.-C., & Choi, K. (2012). Area-efficient parallel FIR digital filter structures for symmetric convolutions based on fast FIR algorithm. IEEE Transactions on Very Large Scale Integration (VLSI) Systems, 20(2), 366–371.

Tsao, Y.-C., & Choi, K. (2012). Area-efficient VLSI implementation for parallel linear-phase FIR digital filters of odd length based on fast FIR algorithm. IEEE Transactions on Circuits and Systems-II Express Briefs, 59(6), 371–376.

Solomon Roach, R., & Nirmal Singh, N. (2016). Design of low power and area efficient ESPFFIR filter using multiple constant multiplier. Rev. Téc. Ing. Univ. Zulia., 39(6), 225–236.

Solomon Roach, R., Nirmal Singh, N., & Rani, C. S. H. (2016). Reconfigurable low power and area efficient ESPFFIR filter using VHBCSE multiplier. Journal of Advances in Chemistry, 12(26), 5763–5769.

Hertley, R. I. (1996). Subexpression sharing in filters using canonic signed digit multipliers. IEEE Transactions on Circuits and Systems II: Analog and Digital Signal Processing, 43(10), 677–688.

Vun, C. H., Premkumar, A. B., & Zhang, W. (2013). A new RNS based DA approach for inner product computation. IEEE Transactions on Circuits and Systems—Part I: Regular Papers, 60(8), 2139–2152.

Gustafsson, O. (2007, May). A difference based adder graph heuristic for multiple constant multiplication problems. In Proceedings—IEEE international symposium on circuits and systems (ISCAS’07), (pp. 1097–1100).

Pan, Y., & Meher, P. K. (2014). Bit-level optimization of adder-trees for multiple constant multiplications for efficient FIR filter implementation. IEEE Transactions on Circuits and Systems I: Regular Papers, 61(2), 455–462.

Qasim, S. M., & Ben Saleh, M. S. (2014). Hardware implementation of microprogrammed controller based digital FIR filter. IAENG Transactions on Engineering Technologies, 247, 29–40.

Author information

Authors and Affiliations

Corresponding author

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Arumugam, N., Paramasivan, B. A Novel Microprogrammed Reconfigurable Parallel VHBCSE Based FIR Filter for Wireless Sensor Nodes. Wireless Pers Commun 115, 2197–2210 (2020). https://doi.org/10.1007/s11277-020-07677-5

Published:

Issue Date:

DOI: https://doi.org/10.1007/s11277-020-07677-5