Abstract

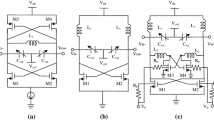

A novel temperature-compensated LC-VCO is presented for RFID applications. By employing a low pass passive filter and an auxiliary varactor loop, the frequency drift is reduced by 70% without using any other active device. The effectiveness of the technique is demonstrated on a frequency synthesizer of a RFID transceiver. The frequency synthesizer is fabricated on a 0.18 μm RF process with a single supply of 1.8 V. The empirical measurements show that the VCO achieves a current consumption of 6 mA, while the passive temperature-compensated circuit does not increase the power consumption. The VCO has a tuning range of 1.6–2.1 GHz and phase a noise of − 124 dBc/Hz at 1 MHz offset from the 1.824 GHz carrier.

Similar content being viewed by others

References

Manetakis, K.., Jessie, D., & Narathong, C. (2004). A CMOS VCO with 48% tuning range for modern broadband systems. In IEEE CICC symposium (pp. 265–268).

Okuno, K., Masaki, K., & Izumi, S., et al. (2015). A 2.23 ps RMS jitter 3 us fast settling ADPLL using temperature compensation PLL controller. In IEEE international conference on electronics (pp. 68–71).

Wu, G., & Sun, K., et al. (2014) A low-voltage and temperature compensated ring VCO design. In Circuits & systems conference (pp. 1–4).

Ravinuthula, V., & Finocchiaro, S. (2016). A low power high performance PLL with temperature compensated VCO in 65 nm CMOS. In Radio frequency integrated circuits symposium (pp. 31–34).

Tanzawa, T., Agawa, K., & Shibayama, H. (2005). A 2.4-GHz temperature-compensated CMOS LC-VCO for low frequency drift low-power direct-modulation GFSK transmitters. IEEE Transactions on Electronics, 88(4), 490–495.

Akima, H., Dec, A., & Merkin, T. (2010). A 10 GHz frequency-drift temperature compensated LC VCO with fast-settling low-noise voltage regulator in 0.13 μm CMOS. In Custom integrated circuits conference (pp. 1–4).

You, Y., Huang, D.., & Chen, J. et al. (2014). A 12 GHz 67% tuning range 0.37 ps RJrms PLL with LC-VCO temperature compensation scheme in 0.13 μm CMOS. In Radio frequency integrated circuits symposium (pp. 101–104).

Liu, T., Wang, X., Wang, R., et al. (2017). A temperature compensated triple-path PLL with KVCO non-linearity desensitization capable of operating at 77 K. IEEE Transactions on Circuits & Systems, 64(11), 2835–2843.

Romano, L., & Romanom R. (2015). Method and apparatus for drift compensation in PLL. US Patents.

Li, Z., Zhuang, Y. Q., & Li, B. (2010). A 2.4 GHz high-linearity low-phase-noise CMOS LC-VCO based on capacitance compensation. Journal of Semiconductor, 31(31), 96–101.

Saeidi, B., Cho, J., & Taskov, G., et al. (2010). A wide-range VCO with optimum temperature adaptive tuning (pp. 337–340). IEEE RFIC.

Zhang, Y., Liu, X., & Rhee, W., et al. (2017). A 0.6 V 50-to-145 MHz PVT tolerant digital PLL with DCO-dedicated ΔΣ LDO and temperature compensation circuits in 65 nm CMOS. In IEEE international symposium on circuits & systems (pp. 1–4).

Li, G., Liu, L., Tang, Y., et al. (2012). A low-phase-noise wide-tuning-range oscillator based on resonant mode switching. IEEE Journal of Solid-State Circuits, 47(6), 1295–1308.

Author information

Authors and Affiliations

Corresponding author

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Liu, Q., Chai, C. A 1.8 GHz temperature drift compensated LC-VCO for RFID transceiver. Analog Integr Circ Sig Process 105, 7–12 (2020). https://doi.org/10.1007/s10470-020-01694-x

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10470-020-01694-x