Abstract

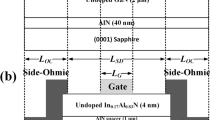

A strained Ge1−x−ySixSny/Ge1−a−bSiaSnb direct type II staggered heterojunction n-channel tunneling field-effect transistor (FET) with a dual-material double gate is proposed herein. A high-K gate dielectric is used to improve the overall device performance. The energy bandgap for strained Ge1−x−ySixSny grown on a relaxed Ge1−a−bSiaSnb layer is determined using the generalized approach of Menendez and Kouvetakis (MK). Poisson’s equation is solved by using a parabolic approximation to determine the surface potential and electric field. The drain current is calculated using the tunneling generation rate obtained from Kane’s model. A significant improvement of the drain current is observed as compared with that of previously reported Si-based TFETs.

Similar content being viewed by others

References

Arun Samuel, T.S., Balamurugan, N.B.: An analytical modeling and simulation of dual material double gate tunnel field effect transistor for low power applications. J. Electr. Eng. Technol. 8, 742–748 (2013)

Taur, Y., Ning, T.H.: Fundamentals of modern VLSI devices. Cambridge University Press, Cambridge (1998)

Anvarifard, M.K., Ramezani, Z., Amiri, I.S., Nejad, A.M.: A nanoscale-modified band energy junctionless transistor with considerable progress on the electrical and frequency issue. Mater. Sci. Semicond Process 107, 104849 (2020)

Shoormasti, A.S., Orouji, A.A., Anvarifard, M.K.: Performance improvement of SiGe based silicon-on-insulator transistor using vertically graded channel approach. Silicon 11, 3021–3030 (2019)

Choi, W.Y., Park, B.-G., Lee, J.D., Liu, T.-J.K.: Tunneling field-effect transistors (TFETs) with subthreshold swing (SS) less than 60 mV/dec. IEEE Electron Device Lett. 28(8), 743–745 (2007). https://doi.org/10.1109/LED.2007.901273

Gandhi, R., Chen, Z., Singh, N., Banerjee, K.: Vertical Si-Nanowire n-type tunneling FETs with low subthreshold swing (~ 50 mV/decade) at room temperature. IEEE Electron Device Lett. 32(4), 437–439 (2011). https://doi.org/10.1109/led.2011.2106757

Zhang, Qin, Zhao, Wei, Seabaugh, Alan: Low subthreshold-swing tunnel transistors. IEEE Electron Device Lett. 27(4), 297–300 (2006). https://doi.org/10.1109/LED.2006.871855

Pal, A., Sachid, A.B., Gossner, H., Rao, V.R.: Insights into the design and optimization of tunnel-FET devices and circuits. IEEE Trans. Electron Devices 58(4), 1045–1053 (2011)

Upasana, Narang, R., Saxena, M., Gupta, M.: “Modeling and TCAD assessment for gate material and gate dielectric engineered TFET architectures: circuit-level investigation for digital applications. IEEE Trans. Electron Devices 62(10), 3348–3356 (2015)

Anvarifard, M.K., Orouji, A.A.: Enhancement of a nanoscale novel Esaki tunneling diode source TFET (ETDS-TFET) for low-voltage operations. Silicon 11, 2547–2556 (2019)

Uddin Shaikh, M.R., Loan, S.A.: Drain-engineered TFET with fully suppressed ambipolarity for high-frequency application. IEEE Trans. Electron Devices 66(4), 1628–1634 (2019)

Garg, S., Saurabh, S.: Improving the scalability of SOI-based tunnel FETs using ground plane in buried oxide. J. Electron Devices Soc. IEEE 7, 435–443 (2019)

Lu, H., Lu, B., Zhang, Y., Zhang, Y., Lv, Z.: Drain current model for double gate tunnel-FETs with in As/Si heterojunction and source-pocket architecture. Nanomaterials 9, 181 (2019)

Ferhati, H., Djeffal, F., Bentrcia, T.: The role of the Ge mole fraction in improving the performance of a nanoscale junctionless tunneling FET: concept and scaling capability. Beilstein J Nanotechnol. 9, 1856–1862 (2018)

Boucart, K., Ionescu, A.M.: Double-gate tunnel FET with high-k gate dielectric. IEEE Trans. Electron Devices 54(7), 1725–1733 (2007)

Saurabh, S., Jagadesh Kumar, M.: Novel attributes of a dual material gate nanoscale tunnel field-effect transistor. IEEE Trans. Electron Devices 58(2), 404–410 (2011)

Nayfeh, O.M., Chleirigh, C.N., Hennessy, J., Gomez, L., Hoyt, J.L., Antoniadis, D.A.: Design of tunneling field-effect transistors using strained-silicon/strained-germanium type-II staggered heterojunctions. IEEE Electron Device Lett. 29(9), 1074–1077 (2008)

Vimala, P., Arun Samuel, T.S., Nirmal, D., Panda, A.K.: Performance enhancement of triple material double gate TFET with heterojunction and heterodielectric. Solid State Electron. Lett. 1(2), 64–72 (2019)

Bhuwalka, K.K., Schulze, J., Eisele, I.: Scaling the vertical tunnel FET with tunnel band gap modulation and gate work function engineering. IEEE Trans. Electron Devices 52(5), 909–917 (2005)

He, G., Atwater, H.A.: Interband transitions in SnxGe1−x alloys. Phys. Rev. Lett. 79, 1937–1940 (1997)

Bauer, M., Taraci, J., Tolle, J., Chizmeshya, A.V.G., Zollner, S., Smith, D.J., Menendez, J., Hu, C., Kouvetakis, J.: Ge–Sn semiconductors for band-gap and lattice engineering. Appl. Phys. Lett. 81(1–3), 2992 (2002)

D’Costa, V.R., Cook, C.S., Birdwell, A.G., Littler, C.L., Canonico, M., Zollner, S., Kouvetakis, J., Menendez, J.: Optical critical points of thin-film Ge1−ySny alloys: a comparative Ge1−ySny/Ge1−xSix study. Phys. Rev. B. 73(1–16), 125207 (2006)

Roucka, R., Xie, J., Kouvetakis, J., Mathews, J., D’Costa, V., Menendez, J., Tolle, J., Yu, S.Q.: Ge1−ySny photoconductor structures at 1.55 μm: from advanced materials to prototype devices. J. Vac. Sci. Technol. B 26, 1952–1959 (2008)

Chizmeshy, A.V.G., Ritter, C., Tolle, J., Cook, C., Menendez, J., Kouvetakis, J.: Fundamental studies of P(GeH3)3, As(GeH3)3, and Sb(GeH3)3: practical n-dopants for new group IV semiconductors. Chem. Mater. 18, 6266–6277 (2006)

Menendez, J., Kouvetakis, J.: Type-I Ge/GeSiSn strained layer heterostructures with a direct Ge band gap. Appl. Phys. Lett. 85, 175–1178 (2004)

Basu, P.K., Mukhopadhyay, B., Basu, R.: Semiconductor laser theory. CRC Press, Boca Raton (2015)

Jiang, L., Gallagher, J.D., Senaratne, C.L., Aoki, T., Mathews, J., Kouvetakis, J., Menendez, J.: Compositional dependence of the direct and indirect band gaps in Ge1_ySny alloys from room temperature photoluminescence: implications for the indirect to direct gap crossover in intrinsic and n-type materials. Semicond. Sci. Technol. 29, 115028 (2014)

Dutt, B., Lin, H., Sukhdeo, D.S., Vulovic, B.M., Gupta, S., Nam, D., Saraswat, K.C., Harris Jr., J.S.: Theoretical analysis of GeSn alloys as a gain medium for a Si-compatible laser. IEEE J. Sel. Top. Quant. Electron. 19, 1502706 (2013)

Dey, S., Mukhopadhyay, B., Sen, G., Basu, P.K.: Type II band alignment in Ge1−x−ySixSny/Ge1−α−βSiαSnβ heterojunctions. Solid State Commun. 270, 155–159 (2018)

Wang, L., Yu, E., Taur, Y., Asbeck, P.: Design of tunneling field effect transistors based on staggered heterojunctions for ultra-low power applications. IEEE Electron Device Lett. 31(5), 431–433 (2010)

Wang, H., Han, G., Liu, Y., Hu, S., Zhang, C., Zhang, J., Hao, Y.: Theoretical investigation of performance enhancement in GeSn/SiGeSn type-II staggered heterojunction tunneling FET. IEEE Trans. Electron Devices 63(1), 303–310 (2016)

Kane, E.O.: Zener tunneling in semiconductors. J. Phys. Chem. Solids 12(2), 181–188 (1960)

Kane, E.O.: Theory of tunneling. J. Appl. Phys. 32(1), 83–91 (1961)

Bardon, M.G., Neves, H.P., Puers, R., Hoof, C.V.: Pseudo-two-dimensional model for double-gate tunnel FETs considering the junctions depletion regions. IEEE Trans. Electron Devices 57(4), 827–834 (2010)

Chuang, S.L.: Physics of photonic devices. Wiley, Hoboken (2009)

Chang, G.-E., Chang, S.-W., Chuang, S.L.: Strain-balanced GezSn1−z−xSix/GeySn1−x−y multiple-quantum-well lasers. IEEE J Quantum Electron 46(12), 1813–1820 (2010)

Chandrasekhar, M., Pollak, F.H.: Phys. Rev. B 15, 2127 (1977)

Van de Walle, C.G.: Band lineups and deformation potentials in the model-solid theory. Phys. Rev. B 39, 1871 (1989)

Garg, Shelly, Saurabh, Sneh: Suppression of ambipolar current in tunnel FETs using drain pocket: proposal and analysis, superlattices and microstructures. Elsevier, Amsterdam (2017)

Shaw, N., Sen, G., Mukhopadhyay, B.: An analytical approach of elimination of ambipolarity of DPDG- TFET using strained type II staggered SiGeSn heterostructure. Superlattices Microstruct. 141, 106488 (2020). https://doi.org/10.1016/j.spmi.2020.106488

Wan, J., Le Royer, C., Zaslavsky, A., Cristoloveanu, S.: Gate-induced drain leakage in FD-SOI devices: what the TFET teaches us about the MOSFET. Microelectron. Eng. 88(7), 1301–1304 (2011)

Liu, X., Hu, H., Wang, M., Miao, Y., Han, G., Wang, B.: Design and theoretical calculation of novel GeSn fully-depleted n-tunneling FET with quantum confinement model for suppression on GIDL effect. Superlattices Microstruct. 118, 266–274 (2018)

Bouhdada, A., Bakkalli, S., Touhami, A.: Modeling of gate induced drain leakage in relation to technological parameters and temperature. Microelectron. Reliabil. 37, 649–652 (1997)

Acknowledgements

The authors thank Prof. Sudakshina Kundu, Ex- Professor, Maulana Abul Kalam Azad University of Technology, West Bengal and Dr. Anirban Bhattacharyya, Assistant Professor, Institute of Radio Physics and Electronics, University of Calcutta for providing insight and expertise that greatly helped in the research.

Author information

Authors and Affiliations

Corresponding author

Ethics declarations

Conflict of interest

The authors declare that they have no conflicts of interest.

Additional information

Publisher’s Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Shaw, N., Mukhopadhyay, B. & Sen, G. Study of the electrical parameters of a dual-material double-gate TFET using a strained type II staggered Ge1−x−ySixSny/Ge1−a−bSiaSnb heterojunction. J Comput Electron 19, 1433–1443 (2020). https://doi.org/10.1007/s10825-020-01540-3

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10825-020-01540-3